Nesta postagem, discutimos as classificações de avalanche de MOSFET e aprendemos como entender essa classificação na folha de dados corretamente, como o parâmetro é testado pelo fabricante e as medidas para proteger os MOSFETs desse fenômeno.

O parâmetro avalanche não só ajuda a verificar a robustez do dispositivo, mas também ajuda a filtrar MOSFETs mais fracos ou mais suscetíveis ou com risco de avaria.

O que é MOSFET Avalanche Rating

A classificação de avalanche do MOSFET é a energia máxima tolerável (milijoule) que um MOSFET pode suportar, quando sua tensão de fonte de drenagem excede o limite de tensão de ruptura máxima (BVDSS).

Este fenômeno normalmente ocorre em circuitos de comutação MOSFET com carga indutiva no terminal de drenagem.

Durante os períodos LIGADO dos ciclos de comutação, o indutor carrega e, durante os períodos DESLIGADO, o indutor libera sua energia armazenada na forma de EMF de volta através da fonte-dreno do MOSFET.

Esta tensão reversa encontra seu caminho através do diodo do corpo do MOSFET, e se seu valor exceder o limite máximo tolerável do dispositivo, faz com que o calor intenso se desenvolva dentro do dispositivo causando danos ou um dano permanente ao dispositivo.

Quando o MOSFET Avalanche foi introduzido

O parâmetro Avalanche Energy e UIS (Unclamped inductive switching) current, de fato, não estava incluído nas planilhas de dados do MOSFET antes da década de 1980.

E foi então que ele evoluiu não apenas para uma especificação de folha de dados, mas um parâmetro que muitos consumidores começaram a exigir que o FET fosse testado antes de passar o dispositivo para produção, especialmente se o MOSFET estiver sendo projetado para fonte de alimentação ou implementações de comutação.

Portanto, foi somente depois dos anos 1980 que o parâmetro avalanche começou a aparecer nas planilhas de dados, e então os técnicos de promoção começaram a entender que quanto maior a classificação da avalanche, mais competitivo o dispositivo parecia ser.

Os engenheiros começaram a determinar técnicas para experimentar o parâmetro ajustando algumas de suas variáveis, que foram usadas no processo de teste.

De modo geral, quanto maior a energia da avalanche, mais durável e forte o MOSFET se torna. Portanto, uma classificação de avalanche maior representa características MOSFET mais fortes.

A maioria das planilhas de dados FET normalmente terá o parâmetro avalanche incluído em sua Tabela de classificações máximas absolutas, que pode ser encontrada diretamente na página de entrada da planilha de dados. Especialmente, você pode visualizar os parâmetros aqui escritos como Corrente de avalanche e Energia de avalanche, Eas.

Portanto, nas planilhas de dados do MOSFET Avalanche Energy é apresentado como a quantidade de energia que o MOSFET é capaz de tolerar enquanto está sendo submetido ao teste de avalanche, ou quando a classificação de tensão de ruptura máxima do MOSFET é ultrapassada.

Avalanche atual e UIS

Essa classificação máxima de tensão de ruptura é determinada por meio do Teste de Corrente de Avalanche, que é realizado por meio de um teste de Chaveamento Indutivo Não Fixado ou do teste UIS.

Portanto, quando os engenheiros discutem sobre a corrente UIS, eles podem estar se referindo à Corrente de Avalanche.

Um teste de chaveamento indutivo não fixado é executado para descobrir a corrente e, portanto, a energia da avalanche que pode acionar a falha do MOSFET.

Como mencionado anteriormente, essas magnitudes ou classificações são extremamente dependentes das especificações de teste, particularmente, o valor do indutor aplicado no momento do teste.

Configuração de teste

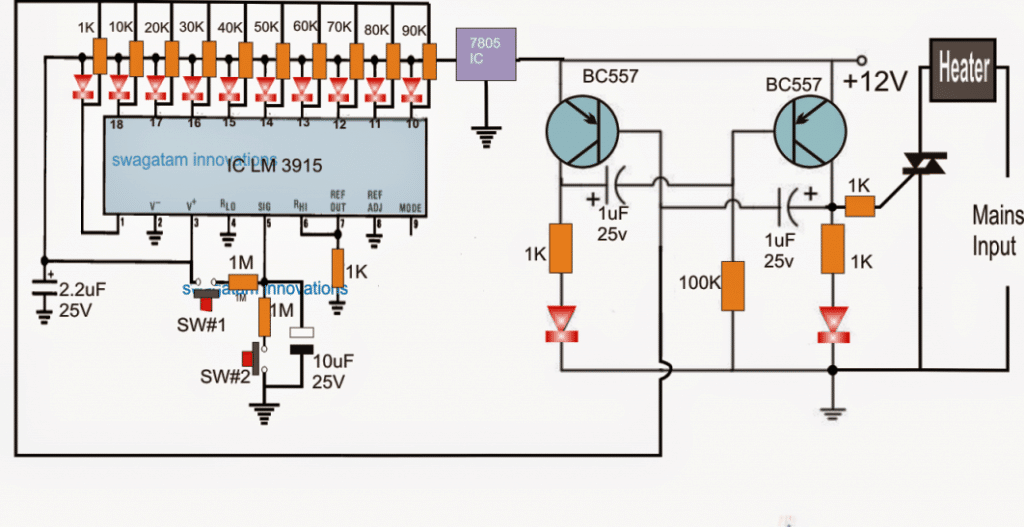

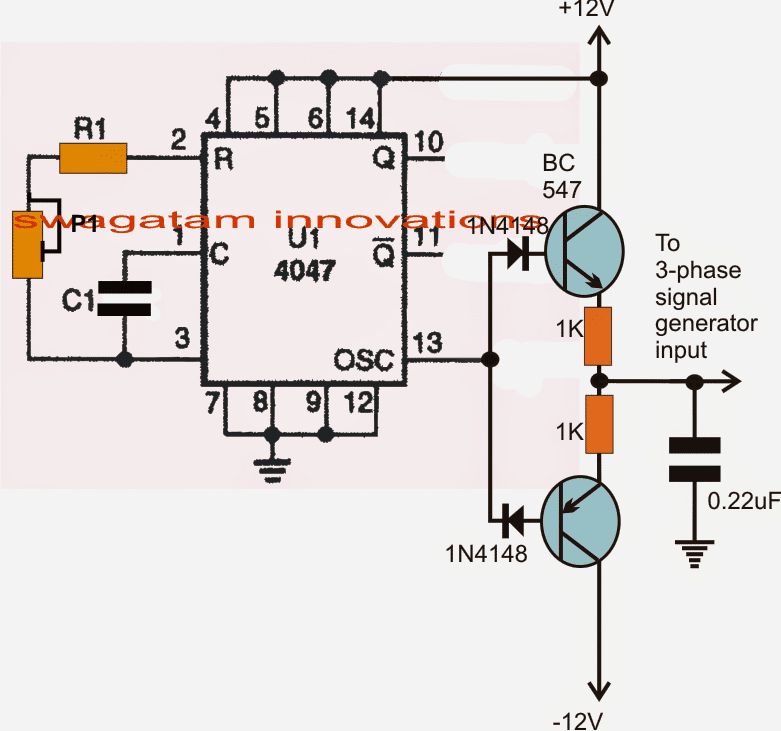

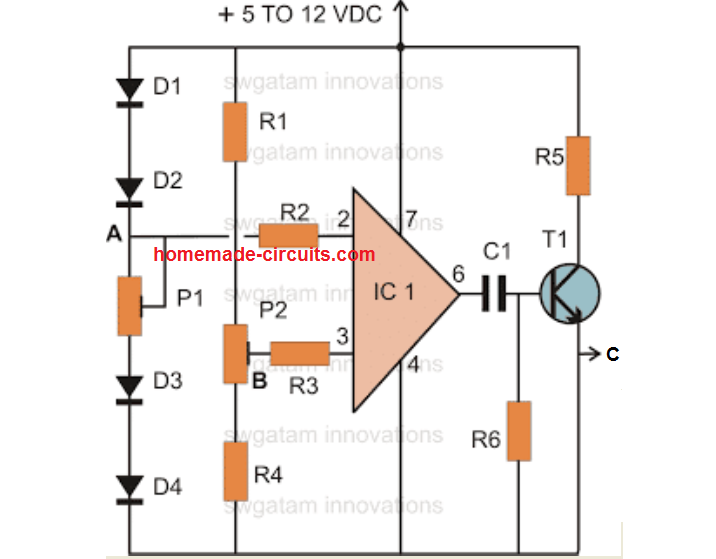

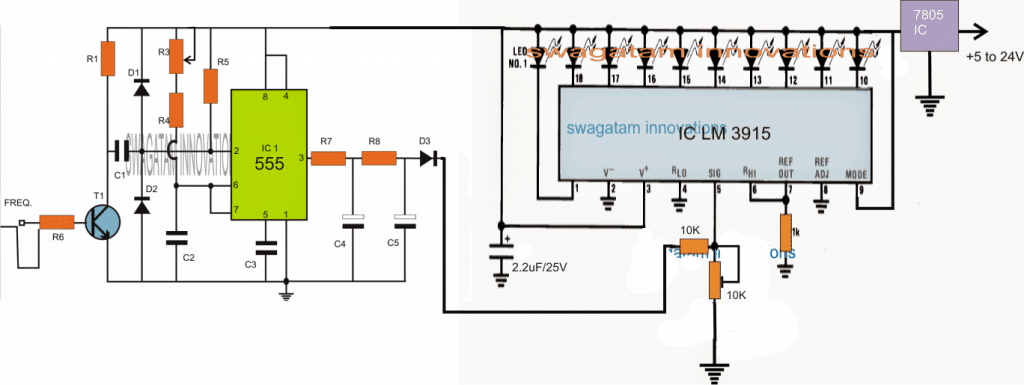

O diagrama a seguir mostra um circuito de teste UIS padrão configurado.

Assim, vemos uma fonte de tensão em série com um indutor, L, que também está em série com o MOSFET em teste. Também podemos ver um driver de porta para o FET cuja saída está em série com um resistor de porta FET R.

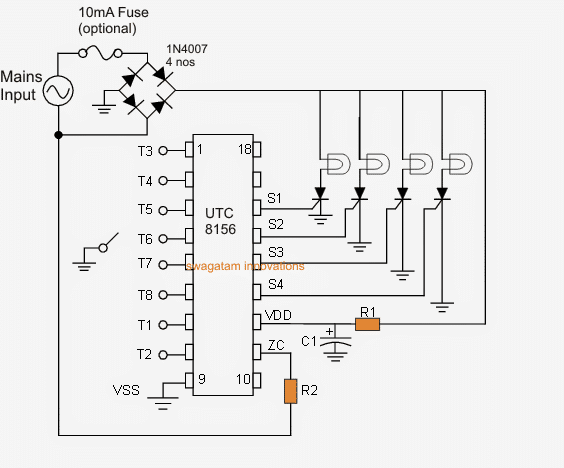

Na imagem abaixo, encontramos o dispositivo controlador LTC55140, que é usado no laboratório de instrumentos do Texas para avaliar as características UIS do FET.

A característica UIS subsequentemente ajuda não apenas a descobrir a classificação da folha de dados do FET, mas também o valor utilizado para digitalizar o FET no procedimento de teste final.

A ferramenta permite ajustar o valor do indutor de carga de 0,2 a 160 millihenries. Permite o ajuste da tensão de dreno do MOSFET em teste de 10 a 150 volts.

Como resultado, isso torna possível rastrear até mesmo os FETs classificados para lidar com apenas 100 volts de tensão de ruptura. E, torna-se possível aplicar correntes de dreno de 0,1 a 200 amperes. E esta é a faixa de corrente UIS que o FET pode ter que tolerar durante o procedimento de teste.

Além disso, a ferramenta permite definir diferentes faixas de temperatura da caixa do MOSFET, de -55 a +150 graus.

Procedimentos de Teste

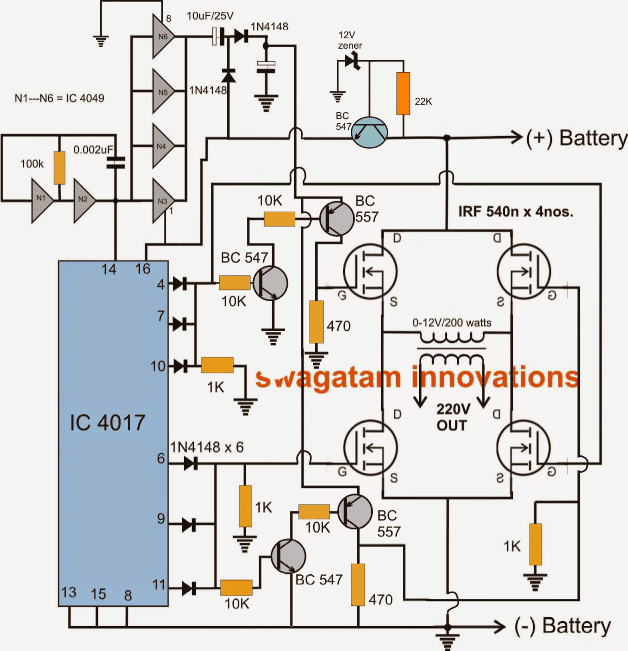

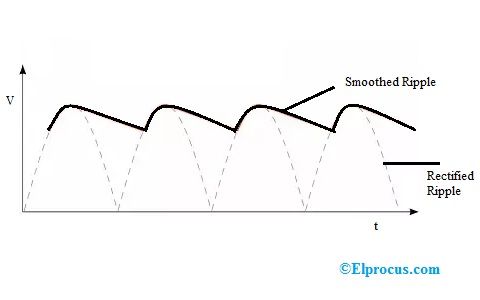

O teste UIS padrão é implementado em 4 estágios, conforme ilustrado na imagem a seguir:

A primeira fase consiste no teste de pré-vazamento, no qual a tensão de alimentação polariza o dreno do FET. Fundamentalmente, a ideia aqui é tentar garantir que o FET esteja funcionando da maneira normal esperada.

Assim, no primeiro estágio, o FET é mantido desligado. Ele mantém a tensão de alimentação bloqueada nos terminais do emissor daim, sem experimentar qualquer tipo de corrente de fuga excessiva fluindo por ele.

No segundo estágio, conhecido como aumento da corrente de avalanche, o FET é ligado, o que faz com que a tensão de dreno caia. Isso faz com que a corrente aumente gradualmente através do indutor com uma di / dt constante. Então, basicamente, neste estágio, o indutor pode carregar.

Na terceira etapa, é realizado o teste de avalanche propriamente dito, onde o FET fica praticamente sujeito à avalanche. Neste estágio, o FET é desligado removendo seu viés de porta. Isso resulta em uma enorme di / dt passando pelo indutor, fazendo com que a tensão de drenagem do FET seja disparada bem acima do limite de tensão de ruptura do FET.

Isso força o FET a passar pela onda de avalanche. Nesse processo, o FET absorve toda a energia gerada pelo indutor, e fica desligado, até que a 4ª etapa seja executada, envolvendo o teste pós-vazamento

Neste 4º estágio, o FET é mais uma vez submetido ao teste de avalanche de repetição, apenas para ter certeza se o MOSFET ainda está se comportando normalmente ou não. Em caso afirmativo, considera-se que o FET passou no teste de avalanche.

Em seguida, o FET tem que passar pelo teste acima muitas mais vezes, em que o nível de tensão UIS é gradualmente aumentado com cada teste, até o nível em que o MOSFET é incapaz de resistir e falha no teste de pós-vazamento. E esse nível de corrente é considerado a capacidade máxima de resistência de corrente UIS do MOSFET.

Calculando a energia de avalanche do MOSFET

Uma vez que a capacidade máxima de manipulação de corrente UIS do MOSFET é atingida, na qual o dispositivo quebra, fica muito mais fácil para os engenheiros estimar a quantidade de energia que é dissipada através do FET durante o processo de avalanche.

Assumindo que toda a energia armazenada no indutor foi dissipada no MOSFET durante a avalanche, esta magnitude de energia pode ser determinada usando a seguinte fórmula:

ÉCOMO= 1 / 2L x IDEdois

ÉCOMOnos dá a magnitude da energia armazenada dentro do indutor, que é igual a 50% do valor da indutância multiplicado pelo quadrado da corrente, fluindo através do indutor.

Posteriormente, foi observado que conforme o valor do indutor foi aumentado, a quantidade de corrente que foi responsável pela quebra do MOSFET diminuiu.

No entanto, esse aumento no tamanho do indutor na verdade compensa essa redução na corrente na fórmula de energia acima de uma forma que o valor da energia literalmente aumenta.

Energia de avalanche ou corrente de avalanche?

Estes são os dois parâmetros, que podem confundir os consumidores, ao verificar a ficha técnica do MOSFET para avaliação de avalanche.

Copyright © Texas Instruments Incorporated

Muitos dos fabricantes de MOSFET testam intencionalmente o MOSFET com indutores maiores, para que sejam capazes de apresentar uma magnitude de energia de avalanche maior, criando a impressão de que o MOSFET foi testado para suportar energias de avalanche enormes e, portanto, tem uma durabilidade aumentada para avalanche.

Mas o método acima de usar indutor maior parece enganoso, é exatamente por isso que os engenheiros da Texas Instruments testam com indutância menor na ordem de 0,1 mH, de modo que o MOSFET em teste está sujeito a uma corrente de avalanche mais alta e níveis extremos de estresse de ruptura.

Portanto, nas planilhas de dados, não é a energia da Avalanche, e sim a corrente da Avalanche que deveria ser maior em quantidade, o que exibe melhor robustez do MOSFET.

Isso torna o teste final altamente rigoroso e permite filtrar o máximo de MOSFETs mais fracos possível.

Este valor de teste não é usado apenas como o valor final antes que o layout FET seja aprovado para a produção, mas também é o valor que é inserido na folha de dados.

Na próxima etapa, o valor de teste acima é reduzido em 65%, para que o usuário final seja capaz de obter uma margem de tolerância mais ampla para seus MOSFETs.

Portanto, por exemplo, se a corrente de avalanche testada foi de 125 Amperes, o valor final que é inserido na folha de dados passa a ser de 81 Amperes, após a redução.

MOSFET Avalanche atual x tempo gasto em avalanche

Outro parâmetro associado ao MOSFET de potência e mencionado nas planilhas de dados, especialmente para os MOSFETs projetados para aplicativos de comutação, é a capacidade de corrente de avalanche versus tempo gasto em avalanche. Este parâmetro é normalmente mostrado em relação à temperatura da caixa do MOSFET em 25 graus. Durante o teste, a temperatura da caixa é aumentada para 125 graus.

Nesta situação, a temperatura da caixa do MOSFET do MOSFET fica muito próxima da temperatura de junção real do molde de silício do MOSFET.

Neste procedimento, conforme a temperatura da junção do dispositivo aumenta, você pode esperar ver uma certa degradação, o que é bastante normal. No entanto, se o resultado mostrar um alto nível de degradação, isso pode indicar os sinais de um dispositivo MOSFET inerentemente fraco.

Portanto, do ponto de vista do projeto, é feita uma tentativa de garantir que a degradação não exceda 30% para um aumento na temperatura da caixa de 25 para 125 graus.

Como proteger o MOSFET da corrente de avalanche

Como aprendemos com as discussões acima, a avalanche em MOSFETs é desenvolvida devido à alternância de EMF indutiva de alta voltagem através do diodo do corpo do MOSFET.

Se esta voltagem EMF de volta exceder a classificação máxima do diodo do corpo, causa extrema geração de calor no dispositivo e danos subsequentes.

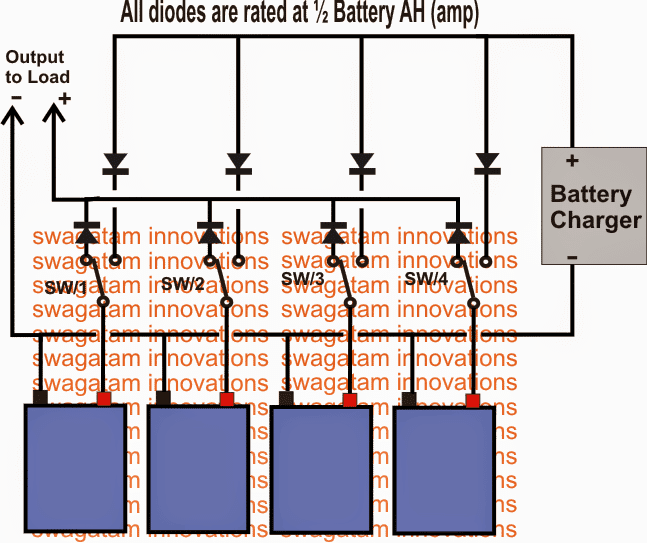

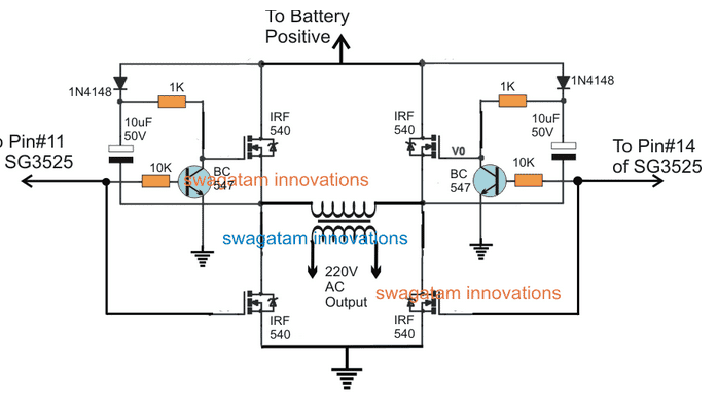

Isso implica que, se a tensão indutiva EMF puder passar por um diodo de bypass externo adequadamente classificado, o dreno-emissor do FET pode ajudar a evitar o fenômeno de avalanche.

O diagrama a seguir sugere o projeto padrão de adição de um diodo dreno-emissor externo para reforçar o diodo interno do corpo do MOSFET.

Cortesia: Avalanche de MOSFET

Anterior: Conversão de ignição por centelha desperdiçada em faísca sequencial, para combustão de alta eficiência Próximo: Circuito UPS Online Simples