Neste artigo, estudaremos um projeto de cronômetro digital configurado em torno do muito popular IC LM555 em conjunto com um IC contador de 4 dígitos com drivers de saída de 7 segmentos multiplexados (MM74C926).

Escrito e enviado por: Jennifer Goldy

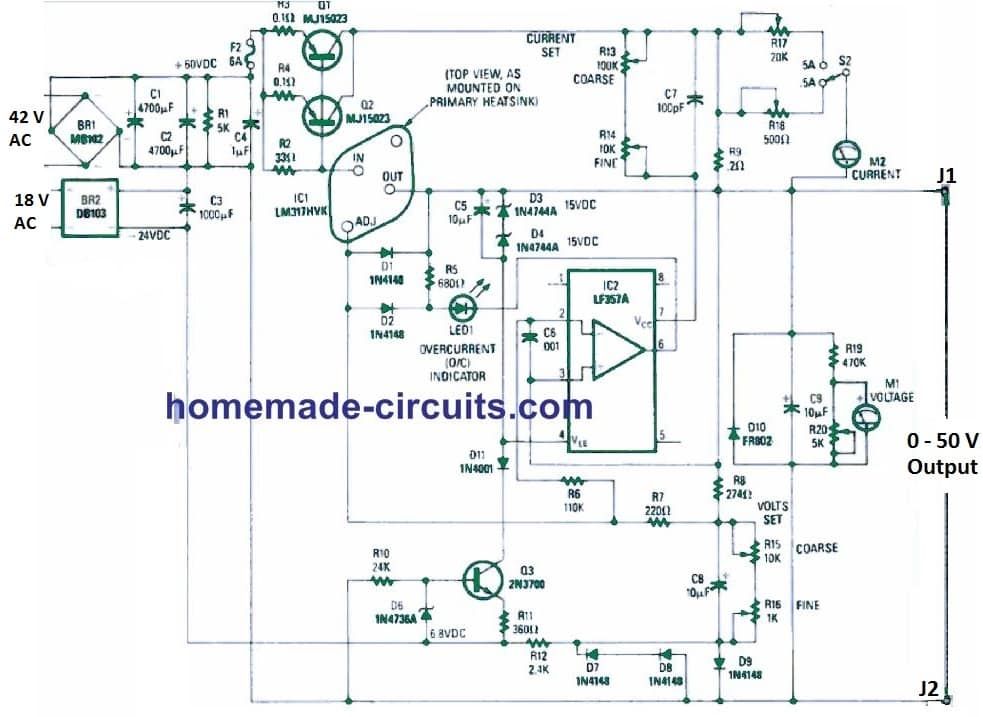

Operação de Circuito

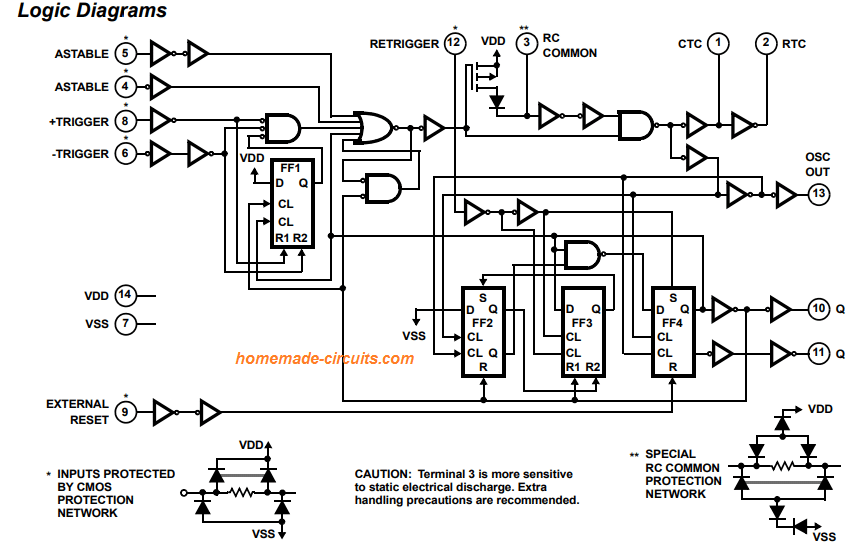

O IC MM74C926 é composto internamente por um contador de 4 dígitos, um estágio de trava de saída, uma saída npn responsável por fornecer redes de driver para catodo comum, display de 7 segmentos e um circuito de multiplexação interno com quatro saídas de multiplexação.

O estágio do circuito de multiplexação também inclui um oscilador de funcionamento livre integrado e não depende de nenhuma rede adicional de geração de frequência externa.

O contador é projetado para prosseguir com um aumento negativo dos sinais do relógio.

O sinal de relógio é fabricado pelo temporizador IC LM555 (IC1) e impresso no pino 12 do IC2.A sinal superior no pino 13 de reset do IC2 redefine o IC para a lógica zero.

O pino 13 de reinicialização está associado a + 5V por meio de um interruptor de reinicialização S3.

No momento em que S2 é pressionado mesmo que por uma fração de segundo, o valor da contagem é processado em uma lógica zero, o transistor T1 responde com um gatilho e reinicializa o IC1.

Isso força o início da contagem em uma situação em que S2 está na condição 'desligado'.

Diagrama de circuito

Um sinal lógico baixo no pino de entrada de habilitação de trava 5 (LE) do IC2 trava a contagem no módulo do contador nas travas de saída do conjunto de chips.

Em um evento quando a chave S2 é ligada, o pino 5 é forçado a baixar e, assim, o número da contagem pode ser salvo na seção de trava do IC.

O pino 6 (DS) de seleção do display verifica se a figura no contador ou a contagem armazenada na trava pode ser exibida ou não no display.

No caso do pino 6 ser mantido baixo, a figura na seção de trava de saída é habilitada para ser exibida, no entanto, se o pino 6 for processado com uma lógica alta, a contagem armazenada no contador é iluminada sobre o display conectado.

Em uma ocasião em que a chave S2 é comutada, a base do transistor pnp T2 é conectada ao aterramento garantindo que ele comece a operar. O emissor de T2 é equipado com o pino DS do IC2.

Consequentemente, sempre que a chave S3 é ligada, o pino de reset 13 do IC2 é acoplado com o negativo através do transistor T1, garantindo que o oscilador seja inibido de gerar pulsos de clock. Esta operação é executada para implementar uma sincronização entre IC1 e IC2.

No primeiro nível, reinicie o módulo para permitir que o visor mostre ‘0000’. Em seguida, desconecte a chave S2 para que o cronômetro inicie a contagem dos períodos. Caso deseje inibir o clocking do chip, basta desligar o controle S2.

A chave rotativa S1 fornecida pode ser optada por selecionar os vários intervalos de tempo diferentes na saída do multivibrador astável (IC1).

O circuito do cronômetro digital proposto funcionará com uma entrada de alimentação de 5V. O circuito pode ser facilmente consertado e construído em um PCB de uso geral.

Você pode colocar todo o circuito em um gabinete metálico com slots construídos para quatro monitores de 7 segmentos, chave rotativa S1, chave liga / desliga S2 e chave de reset S3 na placa do painel do gabinete selecionado.

Anterior: Relógio digital simples usando circuito LM8650 IC Próximo: Como fazer a interface do Arduino PWM com qualquer inversor