No nosso dia a dia, nos deparamos com vários tipos de aparelhos eletrônicos. Uma das tecnologias que revolucionaram a produção de eletrônicos é “ Circuito integrado “. Essa tecnologia reduziu o tamanho dos produtos eletrônicos, aumentando a densidade de portas lógicas por chip. Hoje temos diferentes tipos e configurações de ICs. Conforme observamos ao redor, descobrimos que alguns ICs podem ser usados apenas para uma aplicação específica, enquanto alguns ICs podem ser reprogramados e usados para várias aplicações. Esses tipos de ICs são denominados ASICs. Mas como eles diferem? Como é possível reprogramá-los? Por que alguns ICs não podem ser reprogramados? Continue para encontrar respostas para essas perguntas.

O que é um ASIC (Circuito Integrado Específico de Aplicativo)?

A forma completa ASIC é Circuito Integrado Específico de Aplicação. Esses circuitos são específicos de aplicação, ou seja, CIs feitos sob medida para uma aplicação particular. Geralmente, são projetados a partir do nível raiz com base nos requisitos do aplicativo específico. Alguns dos básicos exemplos de circuitos integrados de aplicações específicas são chips usados em brinquedos, o chip usado para interface de memória e microprocessador etc ... Esses chips podem ser usados apenas para aquele aplicativo para o qual foram projetados. Presumivelmente, estes tipos de ICs são preferidos apenas para aqueles produtos que têm uma grande corrida de produção. Como os ASICs são projetados desde o nível raiz, eles têm alto custo e são recomendados apenas para produções de alto volume.

A principal vantagem do ASIC é o tamanho reduzido do chip, já que um grande número de unidades funcionais de um circuito é construído sobre um único chip. ASIC moderno geralmente inclui um 32-bit microprocessador , blocos de memória, circuitos de rede, etc ... Esse tipo de ASICs é conhecido como Sistema no Chip . Com o desenvolvimento da tecnologia de fabricação e o aumento da pesquisa em métodos de projeto, são desenvolvidos ASICs com diferentes níveis de customização.

Tipos de ASIC

ASICs são categorizados com base na quantidade de customização que um programador pode fazer em um chip.

Tipos de ASICs

Full Custom

Neste tipo de projeto, todas as células lógicas são feitas sob medida para aplicações específicas. o projetista tem que fazer especialmente as células lógicas para os circuitos. Todas as camadas de máscara para interconexão são personalizadas. Portanto, o programador não pode alterar as interconexões do chip e, enquanto programa, ele deve estar ciente do layout do circuito.

Um dos melhores exemplos de ASIC totalmente personalizado é um microprocessador. Esse tipo de personalização permite que os projetistas construam vários circuitos analógicos, células de memória otimizadas ou estruturas mecânicas em um único IC. Este ASIC é caro e consome muito tempo de fabricação e design. O tempo necessário para projetar esses ICs é de cerca de oito semanas.

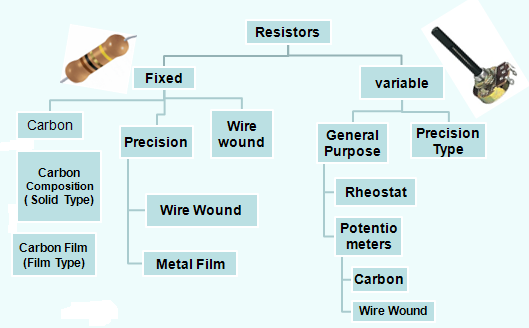

Eles geralmente são destinados a aplicativos de alto nível. Desempenho máximo, área minimizada e maior grau de flexibilidade são os principais recursos do design totalmente personalizado. Eventualmente, o risco é alto no projeto, pois as células lógicas, resistores, etc ... elementos de circuito usados não são pré-testados.

Semi-Custom

Neste tipo de projeto, as células lógicas são retiradas de bibliotecas padrão. eles não são feitos à mão como no design totalmente personalizado. Algumas máscaras são personalizadas, enquanto outras são retiradas da biblioteca predefinida. Com base no tipo de células lógicas retiradas da biblioteca e na quantidade de personalização permitida para interconexões, esses ASICs são divididos em dois tipos - ASIC baseado em célula padrão e ASIC baseado em Gate Array.

1). ASIC baseado em célula padrão

Para conhecer esses IC primeiro, vamos entender o que uma biblioteca de células padrão representa. Algumas das células lógicas, como AND gates, OR gates , multiplexadores, sandálias de dedo são predefinidos por designers usando diferentes configurações, padronizadas e armazenadas na forma de uma biblioteca. Esta coleção é conhecida como biblioteca de células padrão.

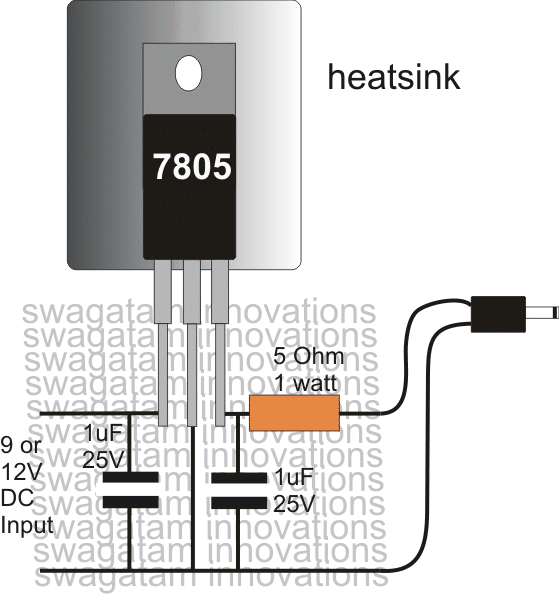

ASIC baseado em células padrão

Em células padrão baseadas em células, as células lógicas ASIC dessas bibliotecas padrão são usadas. No chip ASIC, a área da célula padrão ou bloco flexível são constituídos por células padrão dispostas na forma de linhas. Junto com esses blocos flexíveis, megacélulas como microcontroladores ou mesmo microprocessadores são usados no chip. Essas megacélulas também são conhecidas como Mega funções, macros de nível de sistema, blocos fixos e blocos padrão funcionais.

A figura acima representa um ASIC de célula padrão com uma única área de célula padrão e quatro blocos fixos. As camadas de máscara são personalizadas. Aqui, o designer pode colocar células padrão em qualquer lugar da matriz. Eles também são conhecidos como C-BIC.

2). ASIC baseado em array de portas

Este tipo de ASIC semipersonalizado tem transistores na pastilha de silício, isto é. o projetista não pode alterar o posicionamento dos transistores presentes na matriz. A matriz de base é o padrão predefinido da matriz de porta e a célula base é a menor célula repetitiva da matriz de base.

O projetista só tem a responsabilidade de alterar a interconexão entre os transistores usando as primeiras camadas de metal do molde. O designer escolhe na biblioteca de matrizes de portas. Eles são freqüentemente chamados de Masked Gate Array. Os ASICs baseados em Gate Array são de três tipos. Eles são Channeled Gate Array, Channel less gate array e um array de gate estruturado.

a) .Channeled Gate Array

Nesse tipo de conjunto de portas, o espaço da fiação é deixado entre as fileiras de transistores. Estes são semelhantes ao CBIC, pois o espaço é deixado para a interconexão entre os blocos, mas nas linhas de células da matriz de portas canalizadas são fixas em altura, enquanto no CBIC este espaço pode ser ajustado.

Channeled Gate Array

Algumas das principais características deste array de portas são: este array de portas usa espaços predefinidos entre as linhas para interconexão. O tempo de fabricação é de dois dias a duas semanas.

b). Channel Less Gate Array

Não há espaço livre para o roteamento entre as fileiras de células, conforme visto na matriz de portas canalizadas. Aqui, o roteamento é feito acima das células do array de portas, pois podemos personalizar a conexão entre o metal 1 e os transistores. Para roteamento, deixamos os transistores no caminho de roteamento sem uso. O lead time de fabricação é de cerca de duas semanas.

Channel Less Gate Array

c). Matriz de portas estruturadas

Este tipo de array de portas tem um bloco embutido junto com linhas de array de portas como visto acima. A matriz de portas estruturadas tem uma eficiência de área maior de CBIC. Assim como a matriz de portas mascaradas, elas têm custo mais baixo e tempo de execução mais rápido. Aqui, o tamanho fixo da função embutida impõe uma limitação no arranjo de portas estruturadas. Por exemplo, esta matriz de portas contém uma área reservada para o controlador de 32k bits, mas se em um aplicativo exigirmos apenas uma área para o controlador de 16k bits, a área restante é desperdiçada. Toda a matriz de portas tem um tempo de resposta de dois dias a duas semanas e todos têm interconexão personalizada.

Matriz de portas estruturadas

ASIC programável

Existem dois tipos de ASICs programáveis. Eles são PLD e FPGA

PLDs (Dispositivos Lógicos Programáveis)

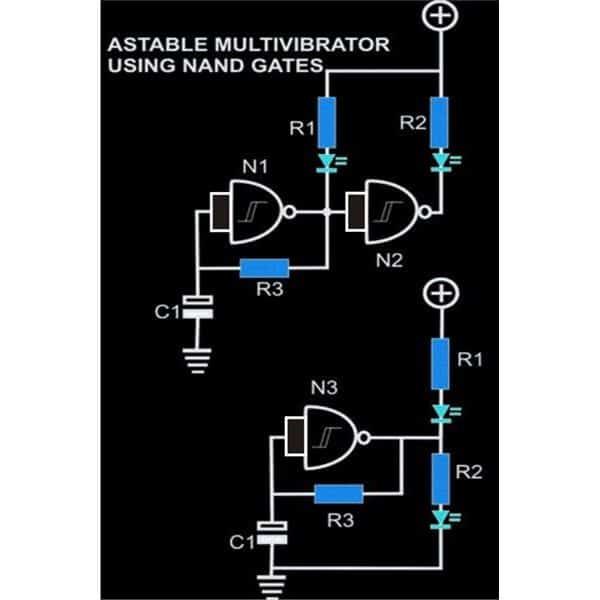

Estas são as células padrão prontamente disponíveis. Podemos programar um PLD para customizar uma parte do aplicativo, para que sejam considerados ASIC. Podemos usar diferentes métodos e softwares para programar um PLD. Eles contêm uma matriz regular de células lógicas, geralmente lógica de matriz programável, juntamente com flip-flops ou travas. Aqui, as interconexões estão presentes como um único bloco grande.

PROM é um exemplo comum deste IC. A EPROM usa transistores MOS como interconexão, portanto, aplicando alta tensão, podemos programá-la. Os PLDs não têm células lógicas personalizadas ou interconexão. Estes têm um design rápido.

Dispositivos Lógicos Programáveis

FPGAs (Field Programmable Gate Array)

Onde os PLDs têm lógica de matriz programável como células lógicas FPGA tem uma disposição semelhante a uma matriz de portas. Os PLDs são menores e menos complexos do que os FPGAs. Devido à sua flexibilidade e características, o FPGA está substituindo TTL em sistemas microeletrônicos. O prazo de entrega do projeto é de apenas algumas horas.

Matriz de portas programáveis em campo

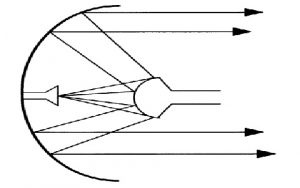

O núcleo consiste em células lógicas básicas programáveis que podem realizar ambos combinacional e lógica sequencial . Podemos programar células lógicas e nos interconectar usando alguns métodos. As células lógicas básicas são circundadas pela matriz de interconexões programáveis e o núcleo é circundado por células de E / S programáveis.

FPGA geralmente é composto de blocos lógicos configuráveis, blocos de E / S configuráveis, interconexões programáveis, circuito de relógio, ALU, memória, decodificadores.

Vimos os diferentes tipos de ASIC disponíveis. Agora vamos entender quando todas essas personalizações e interconexões são feitas durante a fabricação.

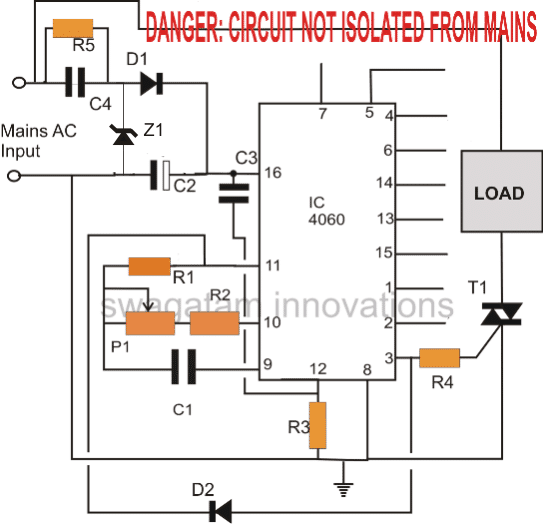

Fluxo de Design de Circuito Integrado Específico de Aplicação (ASIC)

O projeto de um ASIC é realizado passo a passo. Esta ordem de etapas é conhecida como Design ASIC Fluxo. As etapas do fluxo de projeto são fornecidas no fluxograma abaixo.

Fluxo de Design ASIC

Design de entrada: Nesta etapa, a microarquitetura do projeto é implementada usando linguagens de descrição de hardware como VHDL, Verilog e System Verilog.

Síntese lógica: Nesta etapa, uma netlist de células lógicas a serem usadas, tipos de interconexões e todas as outras partes necessárias para a aplicação é preparada usando HDL.

Particionamento do sistema: Nesta etapa, dividimos a matriz de grande porte em peças de tamanho ASIC.

Simulação de pré-layout: Nesta etapa, é feito um teste de simulação para verificar se o projeto contém algum erro.

Planejamento do piso: Nesta etapa, os blocos da netlist são organizados no chip.

Posicionamento: Nesta etapa, a localização das células dentro do bloco é decidida.

Roteamento: Nesta etapa, as conexões são traçadas entre blocos e células. Extração: nesta etapa, determinamos as propriedades elétricas como valor de resistência e valor de capacitância de interconexão.

Simulação pós-layout: Antes do envio do modelo para fabricação esta simulação é feita para verificar se o sistema funciona corretamente junto com uma carga de interconexão.

Exemplos de ASIC

Tendo conhecido as diferentes características do ASIC, vamos agora ver alguns exemplos de ASIC.

ASIC baseado em células padrão: LCB 300k, 500k da LSI Logic Company, SIG1, 2, 3 famílias da ABB Hafo Inc., GCS90K da GCS Plessey.

Produtos Gate Array: AUA20K da Harris Semiconductor, SCX6Bxx da National Semiconductors, famílias TGC / TEC da Texas Instruments.

Produtos PLD: Família PAL de Micro Dispositivos Avançados, família GAL da Philips Semiconductors, XC7300 e EPLD da XILINX.

Produtos FPGA: XC2000, XC3000, XC4000, XC5000 series de XILINX, pASIC1 de QuickLogic, MAX5000 de Altera.

Aplicações de ASIC

A exclusividade do ASIC revolucionou a maneira como os eletrônicos são fabricados. Isso reduziu os tamanhos de matriz, aumentando a densidade de portas lógicas por chip. ASICs são geralmente preferidos para aplicativos de alto nível. O chip ASIC é usado como núcleos IP para satélites, fabricação de ROM, Microcontrolador e vários tipos de aplicações nos setores médico e de pesquisa. Uma das aplicações de tendência da ASIC é BITCOIN MINER.

Bitcoin Miner

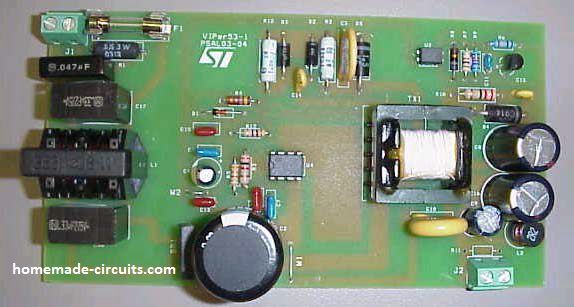

A mineração de criptomoedas requer maior potência e hardware de alta velocidade. Uma CPU de uso geral não pode fornecer tal capacidade de computação superior em alta velocidade. Os mineiros de bitcoin ASIC são chips embutidos em placas-mãe especialmente projetadas e suprimentos de energia , construído em uma única unidade. É um hardware projetado propositalmente até o nível de chip para mineração de bitcoin. Essas unidades podem executar o algoritmo de apenas uma única criptomoeda. Para um tipo diferente de criptomoeda, presumivelmente, precisamos de outro minerador.

Vantagens e desvantagens do ASIC

O vantagens do ASIC inclui o seguinte.

- O tamanho pequeno do ASIC o torna uma escolha ideal para sistemas maiores e sofisticados.

- Como um grande número de circuitos construídos sobre um único chip, isso causa aplicações de alta velocidade.

- ASIC tem baixo consumo de energia.

- Como eles são o sistema no chip, os circuitos estão presentes lado a lado. Portanto, um roteamento mínimo é necessário para conectar vários circuitos.

- ASIC não tem problemas de tempo e configuração de pós-produção.

O desvantagens do ASIC inclui o seguinte.

- Por serem chips personalizados, eles oferecem baixa flexibilidade de programação.

- Como esses chips precisam ser projetados desde o nível raiz, eles têm um alto custo por unidade.

- ASIC tem maior tempo de margem de mercado.

ASIC vs FPGA

A diferença entre ASIC e FPGA inclui o seguinte.

ASIC | FPGA |

| Não reprogramável | Reprogramável |

| Preferido para produções de alto volume | Preferido para produções de baixo volume |

| Estes são específicos do aplicativo | Usado como protótipos de um sistema |

| Eficiente em energia requer menos energia | Menos eficiência energética requer mais energia |

| Esses são circuitos permanentes que não podem ser atualizados de vez em quando. | Altamente adequado para aplicações em que o circuito deve ser atualizado periodicamente, como chips de telefone celular, estações base, etc. |

Portanto, trata-se de uma visão geral de Circuito Integrado Específico de Aplicação . A invenção do ASIC causou uma mudança tremenda na maneira como a eletrônica é usada. Usamos ASIC em nossa vida diária na forma de várias aplicações. Quais aplicativos de ASIC você encontrou? Com que tipo de ASIC você trabalhou?