Diferentes tipos de sistemas digitais são construídos a partir de muito poucos tipos de configurações básicas de rede, como porta AND, porta NAND ou porta, etc ... Esses circuitos elementares são usados repetidamente em várias combinações topológicas. Além de realizar a lógica, os sistemas digitais também devem armazenar números binários. Para essas células de memória, também conhecidas como CHINELO DE DEDO' s são projetados. Para executar algumas funções, como adição binária. Portanto, para desempenhar tais funções, combinações de portas lógicas e os FLIP-FLOPs são projetados sobre um IC de chip único. Esses ICs formam os blocos de construção práticos dos sistemas digitais. Um desses blocos de construção usados para adição binária é o Carry Look-ahead Adder.

O que é um Carry Look-ahead Adder?

Um computador digital deve conter circuitos que podem realizar operações aritméticas, como adição, subtração, multiplicação e divisão. Entre elas, adição e subtração são as operações básicas, enquanto a multiplicação e a divisão são a adição e subtração repetidas, respectivamente.

Para realizar essas operações, 'circuitos somadores' são implementados usando portas lógicas básicas. Circuitos somadores são evoluídos como meio-somador, somador total, somador ondulado e somador antecipado de transporte.

Entre esses, o Carry Look-ahead Adder é o circuito de somador mais rápido. Ele reduz o atraso de propagação, que ocorre durante a adição, usando circuitos de hardware mais complexos. Ele é projetado transformando o circuito do somador de ripple-carry de modo que a lógica de carry do somador seja alterada para uma lógica de dois níveis.

4 bits Carry Look-ahead Adder

Em somadores paralelos, a saída de transporte de cada somador completo é fornecida como uma entrada de transporte para o próximo estado de ordem superior. Portanto, com esses somadores não é possível produzir saídas de transporte e soma de qualquer estado, a menos que uma entrada de transporte esteja disponível para aquele estado.

Portanto, para que a computação ocorra, o circuito precisa esperar até que o bit de transporte seja propagado para todos os estados. Isso induz o atraso de propagação de transporte no circuito.

4-bit-Ripple-Carry-Adder

Considere o circuito somador de transporte de ondulação de 4 bits acima. Aqui, a soma S3 pode ser produzida assim que as entradas A3 e B3 forem fornecidas. Mas o carry C3 não pode ser calculado até que o bit de transporte C2 seja aplicado, enquanto que C2 depende de C1. Portanto, para produzir resultados finais de estado estacionário, o carry deve se propagar por todos os estados. Isso aumenta o atraso de propagação de transporte do circuito.

O atraso de propagação do somador é calculado como “o atraso de propagação de cada porta vezes o número de estágios no circuito”. Para o cálculo de um grande número de bits, mais estágios devem ser adicionados, o que torna o atraso muito pior. Portanto, para resolver essa situação, foi introduzido o Carry Look-ahead Adder.

Para compreender o funcionamento de um Carry Look-ahead Adder, um Carry Look-ahead Adder de 4 bits é descrito abaixo.

Diagrama Lógico-Adder-Carry-Look ahead de 4 bits

Nesse somador, a entrada de transporte em qualquer estágio do somador é independente dos bits de transporte gerados nos estágios independentes. Aqui, a saída de qualquer estágio depende apenas dos bits que são adicionados nos estágios anteriores e da entrada de transporte fornecida no estágio inicial. Conseqüentemente, o circuito em qualquer estágio não precisa esperar pela geração do bit de transporte do estágio anterior e o bit de transporte pode ser avaliado a qualquer momento.

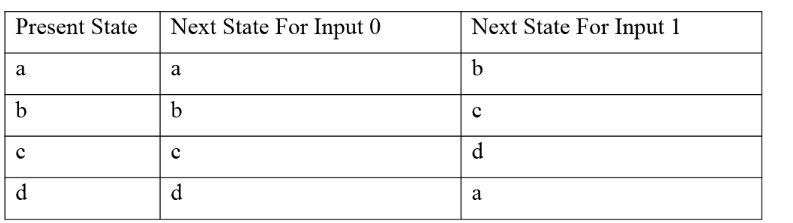

Tabela da verdade de Carry Look-ahead Adder

Para derivar a tabela verdade deste somador, dois novos termos são introduzidos - Carry gera e carrega propaga. Carry gera Gi = 1 sempre que houver um carry Ci + 1 gerado. Depende das entradas Ai e Bi. Gi é 1 quando Ai e Bi são 1. Portanto, Gi é calculado como Gi = Ai. Bi.

O transporte Pi propagado está associado à propagação do transporte de Ci para Ci + 1. É calculado como Pi = Ai ⊕ Bi. A tabela verdade deste somador pode ser derivada da modificação da tabela verdade de um somador completo.

Usando os termos Gi e Pi, Sum Si e Carry Ci + 1 são dados como abaixo -

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Portanto, os bits de transporte C1, C2, C3 e C4 podem ser calculados como

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Pode-se observar pelas equações que o carry Ci + 1 depende apenas do carry C0, não dos bits de carry intermediários.

Carry-Look-ahead-Adder-Truth-Table

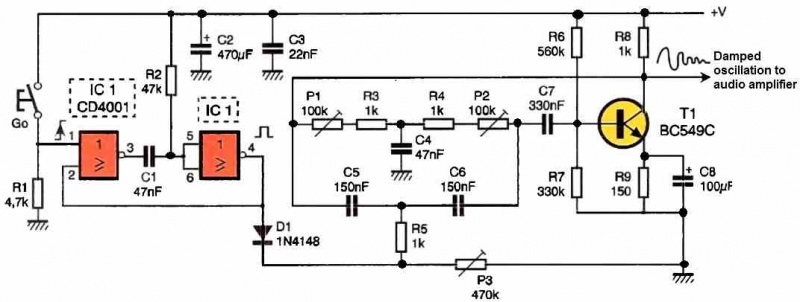

Diagrama de circuito

As equações acima são implementadas usando circuitos combinacionais de dois níveis junto com portas AND, OR, onde as portas são assumidas como tendo múltiplas entradas.

Carry-Output-Generation-Circuit-of-Carry-Look-ahead-Adder

O circuito Carry Look-ahead Adder para 4 bits é fornecido abaixo.

4-bit-Carry-Look-ahead-Adder-Circuit-Diagram

Os circuitos de somador antecipado Carry de 8 e 16 bits podem ser projetados ao colocar em cascata o circuito somador de 4 bits com lógica de transporte.

Vantagens do Carry Look-ahead Adder

Neste somador, o atraso de propagação é reduzido. A saída de transporte em qualquer estágio depende apenas do bit de transporte inicial do estágio inicial. Usando este somador, é possível calcular os resultados intermediários. Este somador é o somador mais rápido usado para computação.

Formulários

Adicionadores de Carry Look-ahead de alta velocidade são usados conforme implementados como ICs. Portanto, é fácil incorporar o somador aos circuitos. Combinando dois ou mais cálculos somadores de funções booleanas de bit mais alto podem ser feitos facilmente. Aqui, o aumento no número de portas também é moderado quando usado para bits maiores.

Para este Adder, há uma compensação entre área e velocidade. Quando usado para cálculos de bits mais altos, fornece alta velocidade, mas a complexidade do circuito também é aumentada, aumentando assim a área ocupada pelo circuito. Este somador é geralmente implementado como módulos de 4 bits que são colocados em cascata quando usados para cálculos superiores. Este somador é mais caro em comparação com outros somadores.

Para computação booleana em computadores, somadores estão sendo usados regularmente. Charles Babbage implementou um mecanismo para antecipar o carry em computadores, para reduzir o atraso causado pelo somadores de transporte de ondulação . Ao projetar um sistema, a velocidade de computação é o maior fator de decisão para um projetista. Em 1957, Gerald B. Rosenberger patenteou o moderno Binary Carry Look-ahead Adder. Com base na análise de atraso de porta e simulação, experimentos estão sendo conduzidos para modificar o circuito deste adicionador para torná-lo ainda mais rápido. Para um somador antecipado de carry de n bits, qual é o atraso de propagação, quando dado um atraso de cada porta é 20?

Crédito da imagem

![Circuito conversor de 24 V para 12 V DC [usando o regulador de comutação]](https://electronics.jf-parede.pt/img/3-phase-power/F1/24-v-to-12-v-dc-converter-circuit-using-switching-regulator-1.jpg)