A postagem detalha os diferentes métodos de configuração de um circuito de correção de fator de potência ou um circuito PFC em projetos SMPS e explica as opções de práticas recomendadas para essas topologias de modo que estejam em conformidade com as diretrizes de restrição de PFC modernas.

Projetar circuitos de fonte de alimentação eficientes nunca foi fácil, no entanto, com o passar do tempo, os pesquisadores foram capazes de resolver a maioria dos problemas preocupantes e, da mesma forma, os projetos SMPS modernos também estão sendo otimizados com os melhores resultados possíveis, graças a os padrões regulatórios emergentes que desempenharam um papel importante na implementação de parâmetros de qualidade mais rígidos para as unidades de fonte de alimentação modernas.

Diretrizes PFC

As modernas restrições de qualidade do fornecimento de energia são estabelecidas de forma bastante agressiva, coletivamente pelos esforços dos fabricantes, fornecedores e outros órgãos governamentais interessados.

Entre os muitos parâmetros de qualidade estabelecidos para os projetos modernos de fonte de alimentação, a correção de correção do fator de potência (PFC), que na verdade está na forma de cancelamento de harmônicos, foi declarada como um requisito obrigatório pelas regras IEC 61000-3-2.

Devido a isso, os projetistas são forçados a enfrentar desafios mais difíceis na concepção de estágios de correção do fator de potência em seus projetos de fonte de alimentação, a fim de atender a essas leis modernas rigorosas, e com as fontes de alimentação ficando cada vez mais formidáveis com suas especificações e faixa de aplicação, estruturando circuitos PFC adequados não está ficando mais fácil para os muitos fabricantes na arena.

Os tutoriais apresentados são especialmente dedicados a todas as associações e profissionais que estão na fabricação ou concepção de flyback SMPS para facilitá-los com os projetos e cálculos de PFC mais ideais de acordo com suas necessidades individuais.

As discussões incluídas nesses tutoriais o ajudarão a projetar circuitos PFC mesmo para unidades significativamente grandes na faixa de até 400 watts, 0,75 amperes.

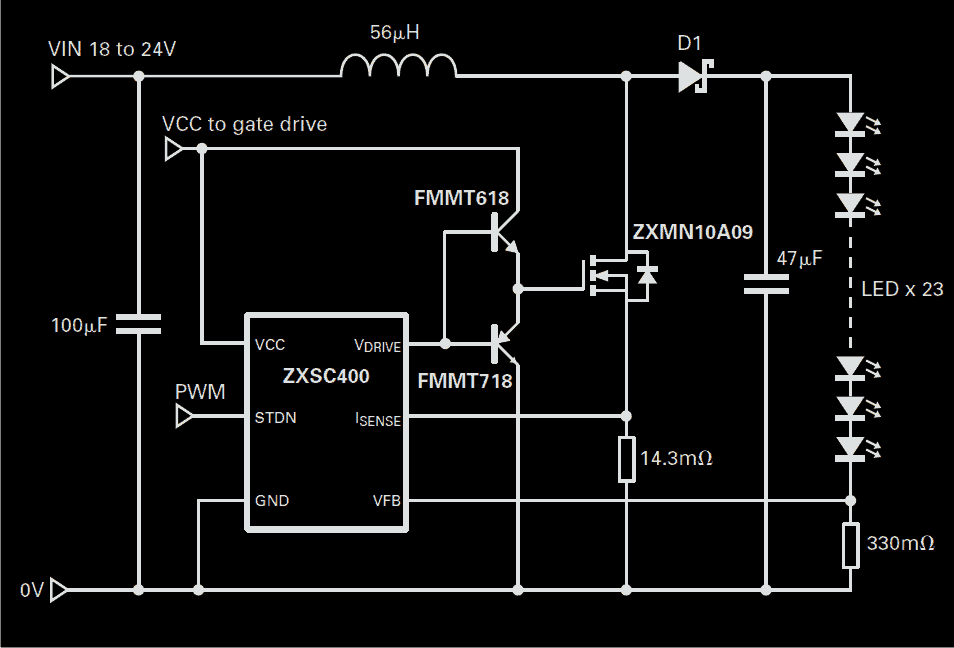

Os leitores também terão a oportunidade de aprender sobre a seleção de conversores isolados de estágio único que também incluem drivers de LED. O tutorial de design passo a passo e as instruções junto com comparações de nível de sistema, os muitos designers ativamente envolvidos no campo da eletrônica de potência serão esclarecidos para faça com a abordagem mais ideal para suas necessidades específicas de aplicação

Objetivo de correção do fator de potência

A otimização do circuito de correção do fator de potência dentro das unidades SMPS modernas (fonte de alimentação comutada) poderia evoluir no passado recente devido ao advento de uma série de circuitos integrados relevantes (ICs) avançados, o que tornou possível estabelecer diferentes projetos de PFC com especificações modos de operação e com capacidade de lidar com desafios individuais.

Com o aumento da gama de topologias SMPS, a complexidade no projeto e implementação de PFC também se agravou nos dias atuais.

No primeiro tutorial aprenderemos a respeito dos detalhes operacionais do projeto que é mais preferido por qualquer profissional nas correções.

Basicamente, a correção do fator de potência ajuda a otimizar a corrente de entrada dentro de fontes de alimentação off-line para que estas sejam capazes de aumentar a potência real da entrada de rede disponível.

De acordo com os requisitos normais, um determinado aparelho elétrico deve emular-se como uma carga de resistividade pura, de modo que permita um consumo de energia reativa zero.

Esta condição resulta na geração de correntes harmônicas de entrada quase nulas, ou seja, permite que a corrente consumida esteja perfeitamente em fase com a tensão de alimentação de entrada que normalmente é em forma de onda senoidal.

Esta conquista permite que o aparelho consuma a “energia real” da rede nos níveis mais ótimos e eficientes, o que por sua vez resulta na minimização do desperdício de eletricidade e no aumento da sua eficiência.

Este uso efetivo da eletricidade não só ajuda o eletrodoméstico a se apresentar da maneira mais eficiente, mas também para as concessionárias e o capital envolvido no processo.

Além disso, o recurso acima permite que as linhas de energia fiquem livres de harmônicos e da interferência resultante nos dispositivos dentro da rede.

Além das vantagens acima mencionadas, a inclusão de um PFC em unidades de fonte de alimentação modernas também é para conformidade com os requisitos regulamentares definidos na Europa e no Japão com o IEC61000-3-2, que todo equipamento elétrico deve se qualificar.

A condição acima mencionada foi regulamentada para a maioria dos aparelhos eletrônicos que podem ser classificados em acima de 75 watts sob os padrões de equipamento da Classe D ou que são ainda mais altos, especificando a maior amplitude dos harmônicos de frequência de linha variando até 39º harmônico.

Além desses padrões, o PFC também é empregado para garantir outras eficiências, como Energy Star 5.0 vital para computadores e Energy Star 2.0 para sistemas de fontes de alimentação e aparelhos de TV desde 2008.

Definição de fator de potência

A correção do PFC ou do fator de potência pode ser definida como a razão entre a potência real e a potência aparente e expressa como:

PF = Potência Real / Potência Aparente, onde a Potência Real é expressa em

Watts, enquanto a potência aparente é expressa em VA.

Nesta expressão, a potência real é determinada como a média do produto instantâneo da corrente e da tensão em uma fase ou ciclo, enquanto a potência aparente é considerada como o valor RMS da corrente vezes a tensão.

Isso sugere que sempre que as contrapartes de corrente e tensão são senoidais e em fase uma com a outra, o fator de potência resultante é 1,0.

No entanto, em uma condição em que a corrente, os parâmetros de tensão são sinusoidais, mas não em fase, dá origem a um fator de potência que é o cosseno do ângulo de fase.

As condições do fator de potência descritas acima se aplicam nos casos em que a tensão e a corrente são ondas senoidais puras, em conjunto com uma situação em que a carga acompanhante é composta por componentes resistivos, indutivos e capacitivos que podem ser todos de natureza não linear, que não está ajustando com os parâmetros de corrente e tensão de entrada.

As topologias SMPS normalmente introduzem impedância não linear na linha de alimentação devido ao tipo de circuito explicado acima.

Como funciona o SMPS

Um circuito SMPS inclui basicamente um estágio retificador na entrada que pode ser uma meia onda ou um retificador de onda completa e um capacitor de filtro complementar para manter a tensão retificada através dele até o nível de pico da onda senoidal de alimentação de entrada até o momento do próximo pico a onda senoidal aparece e repete o ciclo de carga desse capacitor, resultando na tensão constante de pico necessária através dele.

Este processo de carregamento do capacitor a cada ciclo de pico da CA exige que a entrada seja dotada de corrente suficiente para atender ao consumo de carga do SMPS, entre esses intervalos de pico.

O ciclo é implementado despejando rapidamente uma grande corrente no capacitor, que é aplicada à carga por meio da descarga até que o próximo ciclo de pico chegue.

Para este padrão desigual de carga e descarga, é recomendado que a corrente de pulso do capacitor seja 15% maior do que o requisito médio da carga.

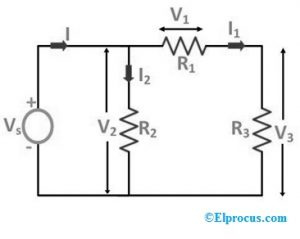

Podemos ver na figura acima que, apesar da quantidade significativa de distorção, os parâmetros de tensão e corrente estão aparentemente em fase um com o outro.

No entanto, se aplicarmos o termo 'cosseno do ângulo de fase' ao acima, daria origem a uma inferência incorreta sobre a fonte de alimentação ter um fator de potência de 1,0

As formas de onda superior e inferior indicam a quantidade de conteúdo harmônico da corrente.

Aqui, o “conteúdo harmônico fundamental” é indicado em comparação com uma amplitude de 100%, enquanto os harmônicos superiores são apresentados como porcentagens suplementares da amplitude fundamental.

No entanto, como a potência real é determinada apenas pelo componente fundamental, enquanto os outros harmônicos suplementares representam apenas a potência aparente, o fator de potência real pode estar bem abaixo de 1,0.

Chamamos esse desvio pelo termo fator de distorção, que é fundamentalmente responsável por dar origem a um fator de potência não unitário nas unidades SMPS.

Expressão para poder real e aparente

Uma expressão geral que trata da conexão entre o poder real e o aparente pode ser dada da seguinte forma:

Onde cosΦ forma o fator de deslocamento emergente do ângulo de fase Φ entre as formas de onda de corrente / tensão e cosΦ significa o fator de distorção.

Referindo-nos ao diagrama abaixo, podemos testemunhar uma situação que mostra uma correção perfeita do fator de potência.

Podemos ver que aqui a forma de onda da corrente replica idealmente a forma de onda da tensão, visto que ambas estão aparentemente funcionando em fase e em sincronia uma com a outra.

Portanto, aqui os harmônicos da corrente de entrada podem ser considerados quase zero.

Correção do fator de potência versus redução de harmônicos

Olhando para as ilustrações anteriores, é evidente que o fator de potência e os harmônicos baixos funcionam em sincronia um com o outro.

É geralmente percebido que se os limites para as respectivas harmônicas forem delineados, pode ajudar a restringir a contaminação da corrente de entrada em linhas de energia, eliminando distúrbios de corrente interferentes com os outros aparelhos nas proximidades.

Portanto, embora o processamento da corrente de entrada possa ser denominado como 'correção do fator de potência', a magnitude do refinamento de saída, embora este processamento seja entendido como conteúdo harmônico de acordo com as diretrizes internacionais.

Para topologias SMPS, é normalmente o elemento de deslocamento que está aproximadamente na unidade, dando origem às seguintes relações entre fator de potência e distorção harmônica.

Na expressão o THD representa a Distorção Harmônica Total como a soma quadrática dos harmônicos prejudiciais sobre o conteúdo fundamental, expressando o peso relativo do conteúdo harmônico associado com referência à contraparte fundamental. A outra equação associa o número absoluto do THD e não na proporção%, expressando que o THD precisa ser essencialmente zero para criar um PF unitário.

Tipos de correção do fator de potência

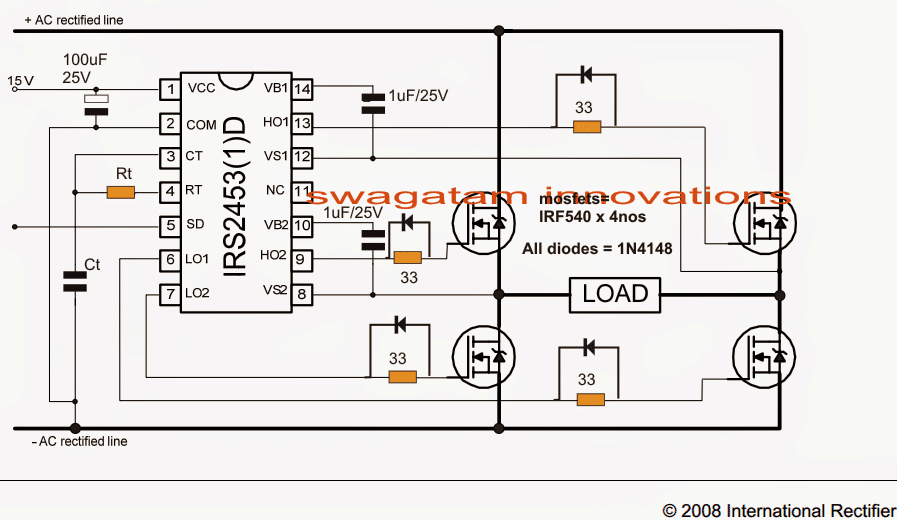

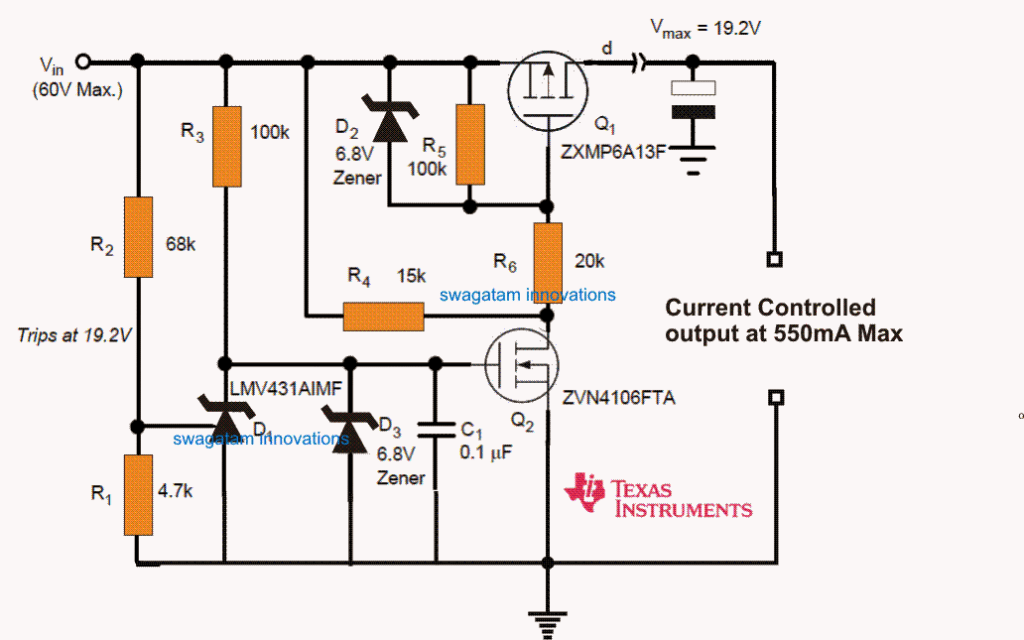

A característica da forma de onda de entrada na figura acima demonstra um tipo 'ativo' típico de correção de fator de potência para um dispositivo SMPS introduzido entre uma configuração de retificador de entrada e um capacitor de filtro, e através de um circuito integrado PFC controlando os procedimentos junto com os circuitos associados para garantindo que a corrente de entrada segue coesivamente a forma de onda da tensão de entrada.

Este tipo de processamento pode ser considerado como o tipo mais prevalente de PFC empregado nos circuitos SMPS modernos, como pode ser testemunhado na figura abaixo.

Dito isto, não é de forma alguma obrigatório que apenas versões 'ativas' usando ICs e semicondutores sejam usados para o PFC proposto. Todas as outras formas de projeto que podem garantir uma quantidade razoável de PFC abaixo dos regulamentos definidos são normalmente bem-vindas.

Foi notado que de fato um único indutor substituindo a posição da contraparte “ativa” é capaz de rejeitar os harmônicos de forma bastante satisfatória, controlando os picos e distribuindo a corrente uniformemente em sincronia com a tensão de entrada de forma bastante eficiente.

Design PFC Passivo

No entanto, esta forma de controle PFC passivo pode exigir um indutor de núcleo de ferro significativamente volumoso e, portanto, pode ser usado para aplicações nas quais a compactação não é um requisito crucial. (página 12)

Um indutor único passivo pode parecer uma solução rápida para PFC, mas para aplicações de alta potência, o tamanho pode começar a ficar desinteressante devido às suas dimensões impraticáveis.

No gráfico abaixo, podemos testemunhar as características de entrada de três números de variantes de SMPS de PC de 250 watts, cada uma representando uma forma de onda atual em um fator de escala equivalente.

Podemos ver facilmente que o resultado obtido de um PFC baseado em indutor passivo é 33% mais alto dos picos de corrente, do que com a contraparte de filtro PFC ativo.

Mesmo que isso possa ser aprovado nos padrões IEC61000-3-2, definitivamente não estará em paridade com a recente regra de requisito 0.9PF mais rigorosa e falharia no nível de aceitação de CQ, definido de acordo com esses novos padrões.

Diagrama de Bloco Básico

Devido à tendência contínua do mercado eletrônico, onde podemos ver os custos do cobre aumentando, juntamente com o aumento no processo de núcleos magnéticos e a introdução de materiais semicondutores modernos e muito mais baratos, não será uma surpresa se notarmos a abordagem PFC ativa ficando extremamente popular do que a contraparte passiva.

E essa tendência pode ser percebida como um crescimento ainda mais forte no futuro próximo, apresentando soluções PFC cada vez mais avançadas e aprimoradas para os muitos designers e fabricantes de SMPS.

Comparando Harmônicos de Linha de Entrada com os Padrões IEC610003-2

Na Figura abaixo, podemos ver traços de três resultados separados de SMPS de PC de 250 watts com referência às restrições IEC6000-3-2. A restrição indicada é válida para todos os dispositivos de classe D, como PCs, TVs e seus monitores.

O limite de conteúdo harmônico mostrado é fixo de acordo com a potência de entrada dos dispositivos. Para produtos relacionados a luzes, como luzes LED, lâmpadas CFL, as restrições de classe C são normalmente seguidas, que são idênticas aos seus limites de potência de entrada.

Outros produtos eletrônicos não convencionais têm seu limite de PFC definido em proporção a uma potência de entrada mínima de 600 watts.

Se olharmos para o traço de PFC passivo, descobrimos que dificilmente está em conformidade com o limite de restrição definido, apenas um tipo de situação toque e vá (no harmônico nº3)

Analisando recursos de PFC passivos

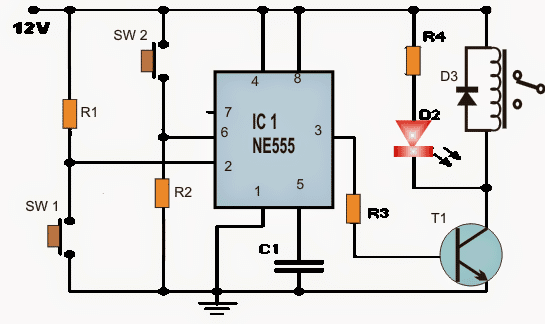

Na figura a seguir podemos ver um exemplo clássico de circuito PFC passivo projetado para uma fonte de alimentação de PC tradicional. O notável aqui é a conexão da derivação central do indutor PFC com a tensão de entrada da linha de entrada.

Enquanto no modo de seleção de 220 V (chave aberta), as duas seções inteiras do indutor são aplicadas com a rede retificadora funcionando como um circuito retificador de ponte completa.

No entanto, no modo 110 V (fechamento da chave), apenas 50% ou metade da bobina é utilizada através da seção do lado esquerdo da bobina que está sendo implementada, enquanto a seção do retificador é agora transformada em um circuito retificador dobrador de meia onda.

Uma vez que a seleção de 220 V é obrigada a gerar cerca de 330 V após a retificação de onda completa, isso forma a entrada do barramento para o SMPS e possui a possibilidade de flutuar significativamente de acordo com a tensão da linha de entrada.

Diagrama de Circuito Exemplo

Embora esse design PFC passivo possa parecer bastante simples e impressionante com seu desempenho, ele pode apresentar algumas desvantagens notáveis.

Junto com a natureza volumosa do PFC, duas outras coisas que afetam seu desempenho são primeiro, a inclusão de um interruptor mecânico que torna o sistema vulnerável a um possível erro humano durante a operação da unidade e também os problemas de desgaste associados.

Em segundo lugar, a tensão da linha não sendo estabilizada resulta em ineficiências relativas nas frentes de eficácia de custo e precisão de conversão de energia DC para DC ligada à saída do PFC.

Controladores de modo de condução crítica (CrM)

O estágio do controlador denominado modo de condução crítica, que também é denominado como modo transicional ou controlador do modo de condução limítrofe (BCM), são configurações de circuitos que podem ser encontradas efetivamente empregadas em aplicações eletrônicas de iluminação. Apesar de serem fáceis de usar, esses controladores são relativamente caros.

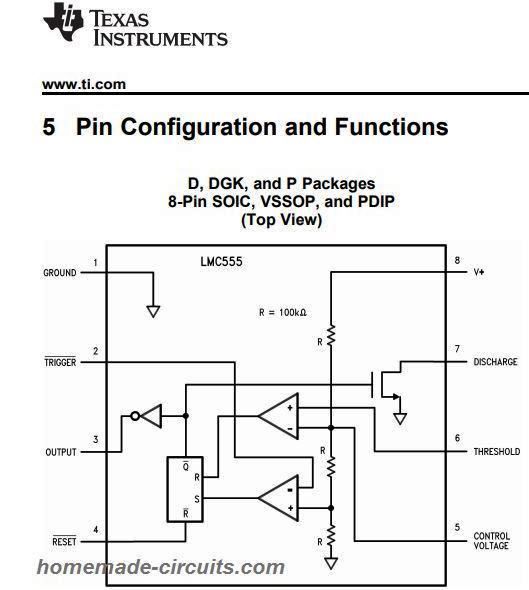

O seguinte diagrama 1-8 demonstra um projeto de circuito controlador de CrM regular.

Normalmente, um PFC controlador de CrM possuirá o tipo de circuito mostrado acima, que pode ser entendido com a ajuda dos seguintes pontos:

Uma entrada de um estágio multiplicador de referência recebe um sinal dimensionado apropriadamente de uma saída de amplificador de erro associada tendo um pólo de baixa frequência.

A outra entrada do multiplicador pode ser vista referenciada com uma tensão fixa CC estabilizada extraída de uma entrada de linha CA retificada.

Assim, a saída resultante do multiplicador é o produto da DC relativa da saída do amplificador com erro e o sinal referenciado na forma de pulsos sinusoidais AC de onda completa da entrada AC.

Esta saída do estágio multiplicador pode ser vista também na forma de pulsos de onda sinusoidal de onda completa, mas adequadamente reduzidos em proporção com o sinal de erro aplicado (fator de ganho) usado como referência para a tensão de entrada.

A amplitude do sinal desta fonte é ajustada apropriadamente para implementar a potência média especificada correta e para garantir uma tensão de saída regulada adequada.

O estágio que é responsável por processar a amplitude da corrente faz com que a corrente flua de acordo com a forma de onda de saída do multiplicador, no entanto, pode-se esperar que a amplitude do sinal da corrente de frequência de linha (após suavização) seja metade daquela referência do estágio multiplicador .

Aqui, as operações por circuitos de modelagem de corrente podem ser entendidas da seguinte forma:

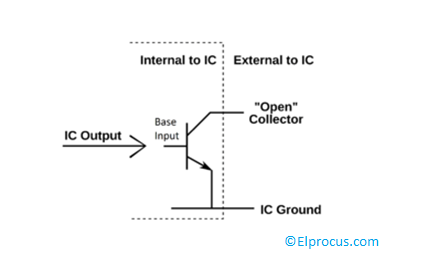

Referindo-se ao diagrama acima, Vref representa o sinal de saída do estágio multiplicador, que é posteriormente alimentado para um dos opamps de um comparador cuja segunda entrada é referenciada com o sinal da forma de onda atual.

Na chave liga / desliga, a corrente através do indutor aumenta lentamente até que o sinal através do shunt alcance o nível Vref.

Isso força o comparador a alterar sua saída de Ligado para Desligado, desligando a alimentação do circuito.

Assim que isso acontece, a tensão que estava gradualmente aumentando através do indutor começa a cair lentamente em direção a zero e, uma vez que chega a zero, a saída do opamp reverte e liga novamente, e o ciclo continua se repetindo.

Como o nome da característica acima significa, o padrão de controle do sistema nunca permite que a corrente do indutor atire acima do limite predeterminado nos modos de chaveamento contínuo e descontínuo.

Este arranjo ajuda a prever e calcular a relação entre o nível de corrente de pico médio da saída resultante do opamp. Como a resposta está na forma de ondas triangulares, a média da forma de onda representa exatamente 50% dos picos reais das formas de onda triangulares.

Isso implica que o valor médio resultante do sinal de corrente das ondas do triângulo seria = Corrente do indutor x R sentido ou simplesmente coloque metade do nível de referência predefinido (Vref) do opamp.

A frequência de um regulador usando o princípio acima dependerá da tensão da linha e da corrente de carga. A frequência pode ser muito mais alta em tensões de linha mais altas e pode variar conforme a variação da entrada de linha.

Modo de condução crítica de freqüência fixada (FCCrM)

Apesar de sua popularidade em várias aplicações de controle PFC de fonte de alimentação industrial, o controlador de CrM explicado acima envolve algumas desvantagens inerentes.

A principal falha deste tipo de controle PFC ativo é sua instabilidade de frequência com relação às condições de linha e carga, que mostra um aumento na frequência com cargas mais leves e tensões de linha mais altas, e também a cada vez que a onda senoidal de entrada se aproxima dos cruzamentos de zero.

Se for feita uma tentativa de retificar este problema adicionando um grampo de frequência, resultará em uma saída com uma forma de onda de corrente distorcida, o que parece inevitável devido ao fato de que “Ton” permanece não ajustado para este procedimento.

No entanto, o desenvolvimento de uma técnica alternativa ajuda a alcançar uma verdadeira correção do fator de potência, mesmo no modo descontínuo (DCM). O princípio de operação pode ser estudado na Figura abaixo e com as equações anexas.

Referindo-se ao diagrama acima, a corrente de pico da bobina pode ser avaliada resolvendo:

A corrente média da bobina com referência ao ciclo de comutação (que também é assumida como a corrente de linha instantânea para o ciclo de comutação dado, devido ao fato de que a frequência de comutação é geralmente mais alta do que a frequência da linha em que as variações da tensão da linha ocorrem ), é expresso com a fórmula:

Combinar a relação acima e a simplificação dos termos dá o seguinte:

A expressão acima indica claramente e implica que, no caso de um método ser implementado em que um algoritmo cuida para manter ton.tciclo / Tsw em um nível constante, isso nos permitiria atingir uma corrente de linha sinusoidal tendo um fator de potência unitário, mesmo em regime descontínuo modo de operação.

Embora as considerações acima revelem alguns benefícios distintos para a técnica do controlador DCM proposta, não parece ser a escolha ideal por causa dos altos níveis de corrente de pico associados, conforme demonstrado na tabela a seguir:

A fim de alcançar as condições de PFC ideais, uma abordagem sensata seria implementar uma condição em que os modos de operação DCM e Crm sejam combinados para tirar o melhor proveito dessas duas contrapartes.

Portanto, quando as condições de carga não são pesadas e o CrM funciona em alta frequência, o circuito vai para o modo de operação DCM, e no caso de quando a corrente de carga é alta, a condição de Crm pode persistir para que os picos de corrente persistam não tendem a cruzar os limites altos indesejáveis.

Esse tipo de otimização entre os dois modos de controle sugeridos pode ser melhor visualizado na figura a seguir, onde os benefícios dos dois modos de controle são combinados para alcançar as soluções mais desejáveis.

Continua modo de condução

O modo de condução contínua de PFC pode se tornar bastante popular em projetos SMPS devido ao seu recurso flexível de aplicação e alcance e às diversas vantagens associadas.

Neste modo, a tensão de pico atual é mantida em um nível inferior, resultando em perdas de comutação minimizadas dentro dos componentes relevantes e, além disso, a ondulação de entrada é processada em um nível mínimo com uma frequência relativamente constante, que por sua vez permite o processo de alisamento muito mais simples para o mesmo.

Os seguintes atributos associados ao tipo CCM de PFC precisam ser discutidos um pouco mais elaboradamente.

Controle Vrms2

Um dos atributos vitais com a maioria dos projetos de PFC aplicados universalmente é o sinal de referência, que precisa ser uma imitação decrescente da volagem de entrada retificada.

Este equivalente retificado minimizado da tensão de entrada é finalmente aplicado no circuito para moldar a forma de onda correta para a corrente de saída.

Conforme discutido acima, um estágio de circuito multiplicador é normalmente empregado para esta operação, mas como sabemos que um estágio de circuito multiplicador poderia ser relativamente menos econômico do que um sistema multiplicador de twn-input tradicional.

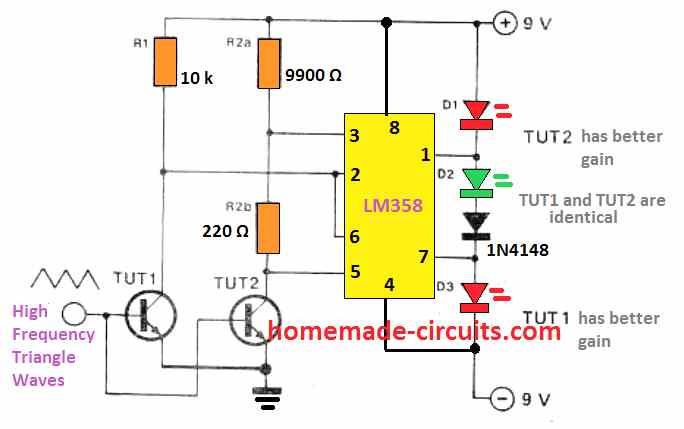

Um layout de exemplo clássico pode ser visto na Figura abaixo, que demonstra uma abordagem PFC de modo contínuo.

Como pode ser visto, aqui o conversor boost é acionado com auxílio de um PWM em modo corrente média, que passa a ser responsável por dimensionar a corrente do indutor (corrente de entrada do conversor), com referência ao sinal de corrente de comando, V (i) , que pode ser visto como o equivalente em escala reduzida da tensão de entrada V (in) para uma proporção de VDIV.

Isso é implementado dividindo o sinal de tensão de erro com o quadrado do sinal de tensão de entrada (suavizado pelo capacitor Cf, a fim de criar um fator de escala simplificado com referência ao nível de tensão de entrada).

Embora você possa achar um pouco estranho ver o sinal de erro sendo dividido pelo quadrado da tensão de entrada, a razão por trás dessa medida é criar um ganho de loop (ou uma resposta dependente transiente) que pode não ser baseado na tensão de entrada desencadeando.

O quadrado da tensão no denominador neutraliza com o valor de Vsin junto com a função de transferência do controle PWM (a proporcionalidade da inclinação do gráfico atual do indutor com a tensão de entrada).

No entanto, uma desvantagem desta forma de PFC é a flexibilidade do multiplicador, o que obriga este estágio a ser um pouco superdimensionado, especialmente nas seções de manuseio de energia do circuito, de modo que sustenta até mesmo os piores cenários de dissipação de energia.

Controle do modo de corrente média

Na figura acima, podemos ver como o sinal de referência produzido a partir do multiplicador V (i) significa a forma da forma de onda e a faixa de escala da corrente de entrada do PFC.

O estágio PWM indicado torna-se responsável por garantir que uma corrente de entrada média esteja em paridade com o valor de referência. O procedimento é executado através de um estágio controlador do modo de corrente média, conforme pode ser visto na figura abaixo.

O controle do modo de corrente média é basicamente configurado para regular a corrente média (entrada / saída) com referência ao sinal de controle Icp, que por sua vez é criado empregando um loop CC de baixa frequência através de um estágio de circuito amplificador de erro, e isso não é nada além a corrente equivalente correspondente ao sinal Vi que é mostrado na figura anterior a este.

O amplificador de corrente de estágio funciona como um integrador de corrente, bem como um amplificador de erro, a fim de regular a forma da forma de onda, enquanto o sinal Icp que é gerado através de Rcp torna-se responsável por executar o controle de tensão de entrada CC.

Para garantir uma resposta linear do amplificador de corrente, sua entrada deve ser semelhante, o que significa que a diferença de potencial gerada em R (shunt) deve ser semelhante à tensão gerada em torno de Rcp, porque não podemos ter uma CC através do entrada do resistor não-inversor do amplificador de corrente.

A saída gerada pelo amplificador de corrente deve ser um sinal de erro de 'baixa frequência' dependendo da corrente média do shunt, bem como do sinal do Isp.

Agora, um oscilador gera um sinal dente de serra que é usado para comparar o sinal acima com ele, assim como feito com o projeto de controle do modo de tensão.

Isso resulta na criação de PWMs determinados pela comparação dos dois sinais mencionados acima.

Soluções PFC Avançadas

Os vários métodos de controles PFC conforme discutido acima (CrM, CCM, DCM) e suas variantes fornecem aos projetistas várias opções de configuração de circuitos PFC.

Porém, apesar dessas opções, a busca consistente por módulos melhores e mais avançados em termos de eficiência tem possibilitado o diagnóstico de projetos mais sofisticados para essas aplicações.

Discutiremos mais sobre isso à medida que este artigo for atualizado com as últimas novidades sobre o assunto.

Anterior: Como selecionar o carregador certo para bateria de íons de lítio Próximo: Circuito Solar E Rickshaw