O IC 4040 é tecnicamente um chip contador de ondulação binário de 12 estágios, em palavras simples, um dispositivo que produzirá uma saída de frequência atrasada calculada em resposta a cada pulso aplicado em sua entrada de relógio. Esse atraso é incrementado na taxa de 2 ^ (n), onde n é a ordem de pinagem na sequência de suas saídas.

Especificações Técnicas Principais

As principais características e especificações do CI podem ser entendidas da seguinte forma:

12 saídas totalmente armazenadas em buffer que dividem os relógios de entrada na taxa 2 ^ (n) onde n = a ordem de pinagem começando de Q0 até Q11.

A seqüência acima das saídas acontece em resposta a cada borda descendente do clock aplicada em sua pinagem CP de entrada de clock. O IC responderá até mesmo a uma queda relativamente lenta do pulso do clock com a mesma eficácia.

Uma única entrada de redefinição mestre assíncrona (MR) que redefine todas as saídas para zero quando uma lógica alta é aplicada, enquanto uma lógica baixa constante permite que o IC permaneça ativo.

O IC torna-se totalmente operacional com Vdd tão baixo quanto 3V e mantém uma característica operacional constante mesmo em tensões em torno de 15V.

Vamos examinar os parâmetros que não devem ser excedidos para o IC 4040

- Tensão de alimentação (Vdd) = Normalmente entre 3 V e 15 V, sendo 18 V o limite máximo.

- Tensão de entrada (Vi) = A tensão que pode ser aplicada nas entradas, como CP, MR etc, deve ser normalmente abaixo de Vdd ou no máximo = Vdd + 0,5V

- Requisito de corrente operacional ideal = 50mA, pois muitas saídas estão envolvidas e cada saída

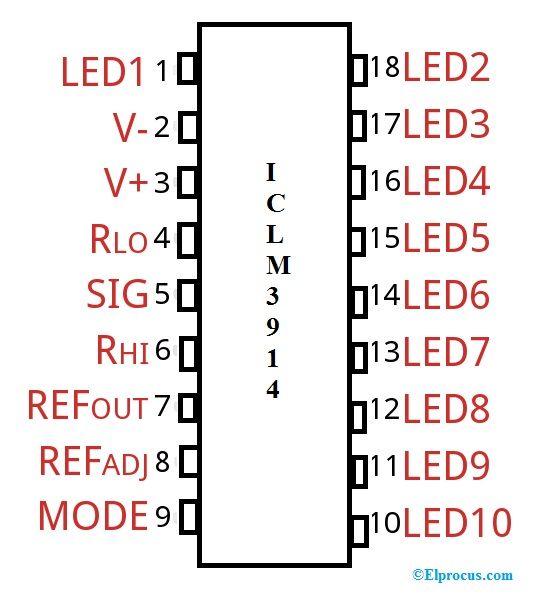

Detalhes de pinagem

O diagrama acima representa a configuração de pinagem do IC 4040, eles podem ser avaliados conforme indicado em:

Pinagens Q0 a Q11 são as saídas do IC.

- Vss é o pino de aterramento.

- Vdd é o pino positivo.

- MR é a pinagem de reinicialização

- CP é a entrada do relógio.

Sequência de tempo

Agora vamos analisar a sequência de tempo de saída do IC 4040. Conforme mostrado no diagrama a seguir, somos capazes de ver e compreender os seguintes detalhes:

Enquanto a entrada MR for alta, as saídas IC não produzem resposta. Assim que fica baixo, o IC começa a responder e a contar o relógio de entrada na entrada do CP.

O primeiro pino de saída Q0 vai alto após 2 ^ (n) clock no CP, que é = 2 ^ (0) = 1, o que significa que Q0 torna-se alto na borda descendente do primeiro pulso e diminui em resposta à borda descendente do relógio subsequente e assim por diante.

Da mesma forma, Q1 aumenta após 2 ^ (1) = 2, o que significa que aumenta assim que uma borda decrescente do segundo relógio é detectada e diminui na borda decrescente do 4º relógio subsequente e assim por diante.

De forma idêntica, Q2 aumenta e diminui após 2 ^ (2) = bordas descendentes do 4º relógio e assim por diante.

A sequência acima é continuada até Q11, em resposta às entradas de relógio sustentado no CP.

Isso significa que se suponha que o CP está sincronizado com um pulso de 1 Hz, Q11 aumentaria após 2 ^ 11 segundos ou após 2048 segundos, que é igual a 34 minutos aproximadamente, imagine a faixa de atraso que você pode alcançar simplesmente aumentando a entrada do relógio em segundos ou talvez por minutos.

Dicas de aplicação

A partir da análise detalhada acima da folha de dados do IC 4040, podemos concluir que o IC é normalmente adequado para todas as aplicações que envolvem requisitos de divisão de frequência ou requisitos de geração de período de tempo atrasado.

Portanto, ele pode se tornar especificamente adequado para aplicações de circuito divisor de frequência, temporizadores de longa duração, piscas e outras aplicações semelhantes.

Anterior: Usando o dissipador de calor de tira de alumínio para LEDs de alta potência em vez de PCB Próximo: Circuito do temporizador do agitador do motor da máquina de lavar