O transistor MOS é o elemento mais fundamental no projeto de circuitos integrados em larga escala. Esses transistores são geralmente classificados em dois tipos PMOS e NMOS. A combinação de transistores NMOS e PMOS é conhecida como transistor CMOS . O diferente portas lógicas e outros dispositivos lógicos digitais implementados devem ter lógica PMOS. Esta tecnologia é barata e tem boa resistência a interferências. Este artigo discute um dos tipos de transistores MOS como um transistor PMOS.

O que é transistor PMOS?

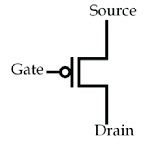

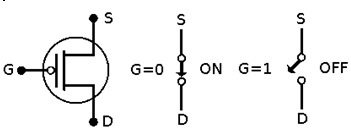

O transistor PMOS ou semicondutor de óxido metálico de canal P é um tipo de transistor em que os dopantes do tipo p são utilizados no canal ou na região do portão. Este transistor é exatamente o inverso do transistor NMOS. Esses transistores possuem três terminais principais; a fonte, o portão e o dreno onde a fonte do transistor é projetada com um substrato tipo p e o terminal de drenagem é projetado com um substrato tipo n. Neste transistor, os portadores de carga como buracos são responsáveis pela condução da corrente. Os símbolos do transistor PMOS são mostrados abaixo.

Como funciona o transistor PMOS?

O funcionamento do transistor tipo p é exatamente o oposto do transistor tipo n. Este transistor formará um circuito aberto sempre que receber uma tensão não desprezível, ou seja, não há fluxo de eletricidade do terminal da porta (G) para a fonte (S). Da mesma forma, este transistor forma um circuito fechado quando atinge uma tensão em torno de 0 volts, o que significa que a corrente flui do terminal do portão (G) para o dreno (D).

Essa bolha também é conhecida como bolha de inversão. Portanto, a principal função deste círculo é inverter o valor da tensão de entrada. Se o terminal do portão fornecer uma tensão 1, este inversor irá alterá-lo para zero e operar o circuito de acordo. Portanto, a função do transistor PMOS e do transistor NMOS é totalmente oposta. Assim que os fundirmos em um único circuito MOS, ele se tornará um circuito CMOS (semicondutor de óxido de metal complementar).

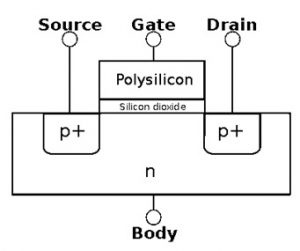

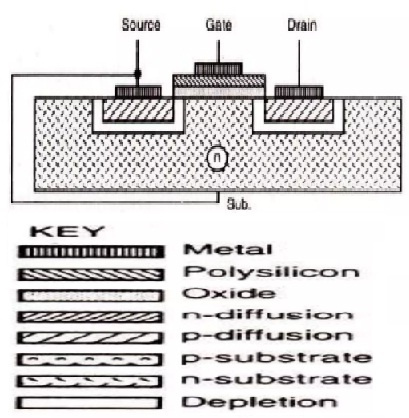

Seção Transversal do Transistor PMOS

A seção transversal do transistor PMOS é mostrada abaixo. Um transistor pMOS é construído com um corpo do tipo n, incluindo duas regiões semicondutoras do tipo p adjacentes à porta. Este transistor tem um portão de controle, conforme mostrado no diagrama, que controla o fluxo de elétrons entre os dois terminais, como fonte e dreno. No transistor pMOS, o corpo é mantido em tensão +ve. Uma vez que o terminal do portão é positivo, os terminais de fonte e dreno são polarizados reversamente. Quando isso acontecer, não haverá fluxo de corrente, então o transistor será desligado.

Uma vez que o fornecimento de tensão no terminal do portão é reduzido, os portadores de carga positiva serão atraídos para a parte inferior da interface Si-SiO2. Sempre que a tensão ficar suficientemente baixa, o canal será invertido e criará um caminho condutor do terminal da fonte para o dreno, permitindo o fluxo de corrente.

Sempre que esses transistores lidam com lógica digital, geralmente há dois valores diferentes apenas como 1 e 0 (ON e OFF). A tensão positiva do transistor é conhecida como VDD, que representa o valor lógico alto (1) nos circuitos digitais. Os níveis de tensão VDD em Lógica TTL eram geralmente em torno de 5V. Atualmente, os transistores não podem realmente suportar tensões tão altas porque normalmente variam de 1,5 V a 3,3 V. A baixa tensão é freqüentemente conhecida como GND ou VSS. Portanto, VSS significa a lógica '0' e também é definido normalmente como 0V.

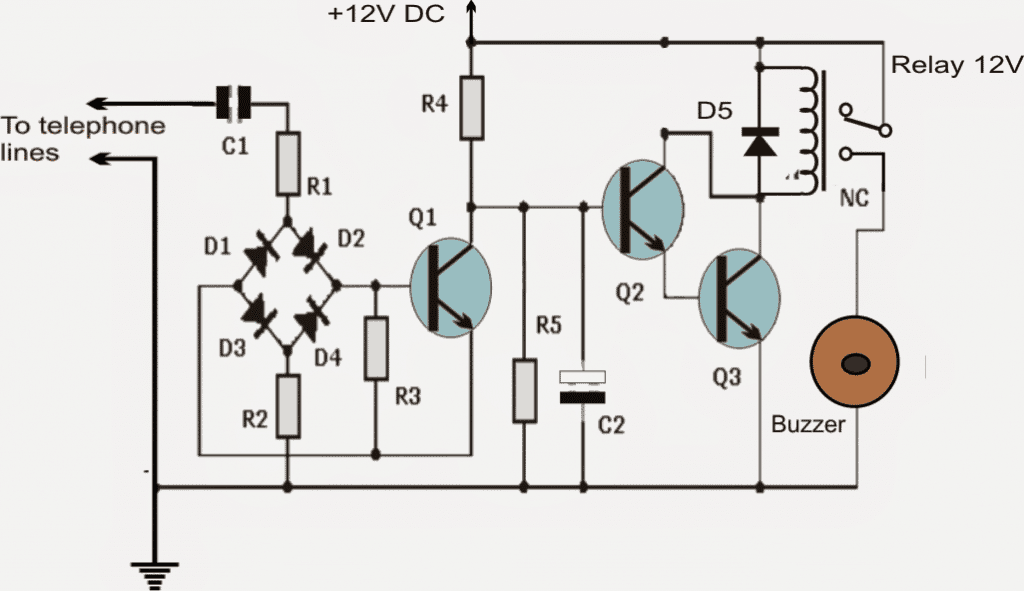

Circuito Transistor PMOS

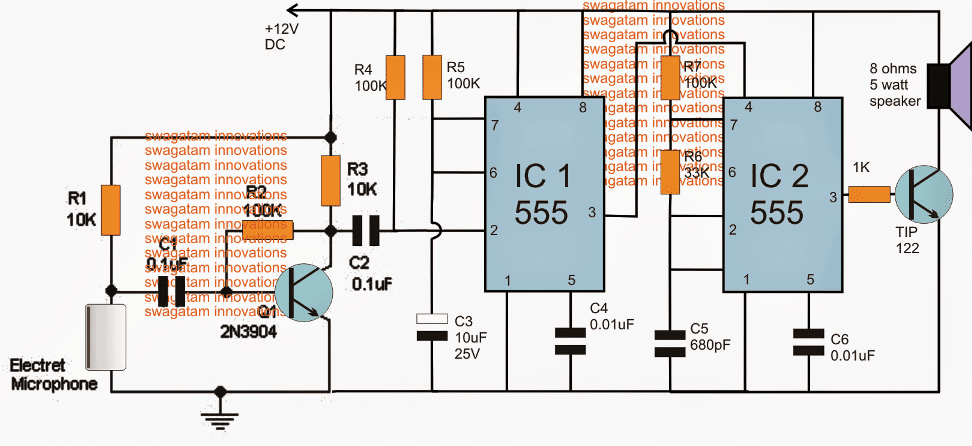

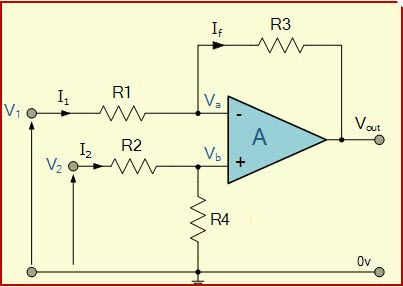

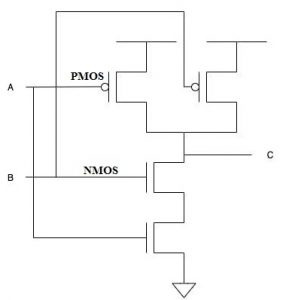

O projeto da porta NAND usando o transistor PMOS e o transistor NMOS é mostrado abaixo. Geralmente, uma porta NAND em eletrônica digital é uma porta lógica que também é chamada de porta NOT-AND. A saída desta porta é baixa (0) somente se as duas entradas forem altas (1) e sua saída for um complemento para uma porta AND. Se qualquer uma das duas entradas for BAIXA (0), ela fornecerá resultados de saída altos.

No circuito lógico abaixo, se a entrada A for 0 e B for 0, então uma entrada de pMOS produzirá '1' e uma entrada de nMOS produzirá '0'. Portanto, esta porta lógica gera um '1' lógico porque está conectada à fonte por um circuito fechado e separada do GND por um circuito aberto.

Quando A é '0' e B' é '1', então uma entrada de pMOS irá gerar um '1' e uma entrada de NMOS irá gerar um '0'. Assim, esta porta produzirá uma porta lógica porque está conectada à fonte por um circuito fechado e separada do GND por um circuito aberto. Quando A é '1' e B é '0', a entrada 'B' do pMOS gerará uma saída alta (1) e a entrada 'B' do NMOS gerará uma saída baixa (0). Portanto, esta porta lógica gerará um 1 lógico porque está conectada à fonte por meio de um circuito fechado e separada do GND por um circuito aberto.

Quando A é '1' e B é '1', então uma entrada de 'pMOS produzirá um zero e uma entrada de nMOS gerará '1'. Consequentemente, devemos verificar a entrada B de pMOS & nMOS também. A entrada B de pMOS gerará um '0' e a entrada B de nMOS gerará um '1'. Portanto, essa porta lógica gerará um '0' lógico porque é separada da fonte por um circuito aberto e conectada ao GND por meio de um circuito fechado.

tabela verdade

A tabela verdade do circuito lógico acima é dada abaixo.

|

UMA |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

A tensão limite do Transistor PMOS é normalmente o 'Vgs' que é necessário para criar o canal conhecido como inversão de canal. Em um transistor PMOS, o substrato e os terminais de origem são simplesmente conectados a 'Vdd'. Se começarmos a reduzir a tensão por referência ao terminal da fonte no terminal do portão de Vdd para um ponto onde você percebe a inversão do canal, nesta posição, se você analisar Vgs e fonte em alto potencial, obterá um valor negativo. Portanto, o transistor PMOS tem um valor Vth negativo.

Processo de Fabricação PMOS

As etapas envolvidas na fabricação do transistor PMOS são discutidas abaixo.

Passo 1:

Uma fina camada de wafer de silício é transformada em material do tipo N simplesmente dopando o material de fósforo.

Passo 2:

Uma espessa camada de dióxido de silício (Sio2) é cultivada em um substrato tipo p completo.

Etapa 3:

Agora a superfície é revestida com um fotorresistente sobre a espessa camada de dióxido de silício.

Passo 4:

Depois disso, essa camada é simplesmente exposta à luz ultravioleta por meio de uma máscara que define as regiões nas quais a difusão deve ocorrer junto com os canais do transistor.

Passo 5:

Essas regiões são gravadas mutuamente com o dióxido de silício subjacente, de modo que a superfície do wafer seja exposta dentro da janela definida pela máscara.

Passo 6:

O fotorresiste restante é destacado e uma fina camada de Sio2 é cultivada tipicamente 0,1 micrômetros em toda a superfície do chip. Depois disso, polissilício é colocado sobre isso para formar a estrutura do portão. Um fotorresiste é colocado sobre toda a camada de polissilício e expõe a luz UV através da máscara2.

Passo 7:

As difusões são alcançadas através do aquecimento do wafer até a temperatura máxima e passagem de gás com as impurezas do tipo p desejadas, como o boro.

Passo 8:

Um dióxido de silício de 1 micrômetro de espessura é cultivado e o material fotorresistente é depositado sobre ele. Exponha a luz ultravioleta com mask3 nas áreas preferidas do portão, fonte e dreno que são gravadas para fazer os cortes de contato.

Passo 9:

Agora, um metal ou alumínio é depositado sobre sua superfície de 1 micrômetro de espessura. Mais uma vez, um material fotorresistente é desenvolvido em todo o metal e exposto à luz UV através da máscara4, que é gravada para formar o design de interconexão necessário. A estrutura PMOS final é mostrada abaixo.

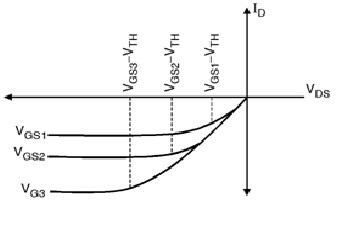

Características do transistor PMOS

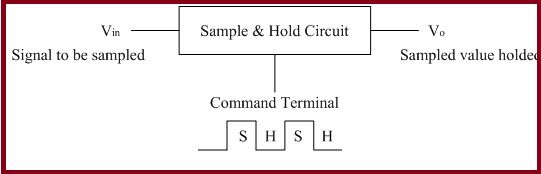

As características I-V do transistor PMOS são mostradas abaixo. Essas características são divididas em duas regiões para obter a relação entre a corrente dreno para fonte (IDS), bem como suas tensões terminais como regiões lineares e de saturação.

Em uma região linear, o IDS aumentará linearmente quando o VDS (tensão do dreno para a fonte) aumentar, enquanto na região de saturação, o IDS é estável e independente do VDS. A principal relação entre o ISD (fonte para drenar a corrente) e suas tensões terminais é derivada por um procedimento semelhante do transistor NMOS. Nesse caso, a única mudança será que os portadores de carga presentes na camada de inversão são simplesmente buracos. Quando os orifícios se movem da fonte para o dreno, o fluxo de corrente também é o mesmo.

Assim, o sinal negativo aparece dentro da equação atual. Além disso, todos os bias aplicados nos terminais do dispositivo são negativos. Assim, as características ID – VDS do transistor PMOS são mostradas abaixo.

A equação da corrente de dreno para o transistor PMOS na região linear é dada como:

ID = – mp Cox

Da mesma forma, a equação de corrente de dreno para o transistor PMOS na região de saturação é dada como:

ID = – mp Cox (VSG – | V TH |p )^2

Onde ‘mp’ é a mobilidade do buraco & ‘|VTH| p' é a tensão limite do transistor PMOS.

Na equação acima, o sinal negativo indicará que o ID( drenar corrente ) flui do dreno (D) para a fonte (S) enquanto os furos fluem na direção oposta. Quando a mobilidade do buraco é baixa em comparação com a mobilidade do elétron, os transistores PMOS sofrem com a capacidade do drive de baixa corrente.

Portanto, trata-se de uma visão geral do transistor PMOS ou transistor mos tipo p - fabricação, circuito e seu funcionamento. PMOS transistores são projetados com uma fonte p, um substrato n e dreno. Os portadores de carga do PMOS são buracos. Este transistor conduz uma vez que a baixa tensão é aplicada no terminal da porta. Os dispositivos baseados em PMOS são menos propensos a interferências em comparação com os dispositivos NMOS. Esses transistores podem ser usados como resistores controlados por tensão, cargas ativas, espelhos de corrente, amplificadores de transimpedância e também usados em chaves e amplificadores de tensão. Aqui está uma pergunta para você, o que é um transistor NMOS?